Lane initialization and reversal – Altera IP Compiler for PCI Express User Manual

Page 187

Chapter 9: Optional Features

9–5

Lane Initialization and Reversal

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

■

For L0s, the connected component and the exit latency of each component

between the root port and endpoint is compared with the endpoint’s acceptable

latency. For example, for an endpoint connected to a root port, if the root port’s L0s

exit latency is 1 µs and the endpoint’s L0s acceptable latency is 512 ns, software

will probably not enable the entry to L0s for the endpoint.

■

For L1, software calculates the L1 exit latency of each link between the endpoint

and the root port, and compares the maximum value with the endpoint’s

acceptable latency. For example, for an endpoint connected to a root port, if the

root port’s L1 exit latency is 1.5 µs and the endpoint’s L1 exit latency is 4 µs, and

the endpoint acceptable latency is 2 µs, the exact L1 exit latency of the link is 4 µs

and software will probably not enable the entry to L1.

Some time adjustment may be necessary if one or more switches are located between

the endpoint and the root port.

1

To maximize performance, Altera recommends that you set L0s and L1 acceptable

latency values to their minimum values.

Lane Initialization and Reversal

Connected PCI Express components need not support the same number of lanes. The

×4 and ×8 IP core in both soft and hard variations support initialization and operation

with components that have 1, 2, or 4 lanes. The ×8 IP core in both soft and hard

variations supports initialization and operation with components that have 1, 2, 4, or

8 lanes.

The hard IP implementation includes lane reversal, which permits the logical reversal

of lane numbers for the ×1, ×2, ×4, and ×8 configurations. The Soft IP implementation

does not support lane reversal but interoperates with other PCI Express endpoints or

root ports that have implemented lane reversal. Lane reversal allows more flexibility

in board layout, reducing the number of signals that must cross over each other when

routing the PCB.

summarizes the lane assignments for normal configuration.

summarizes the lane assignments with lane reversal.

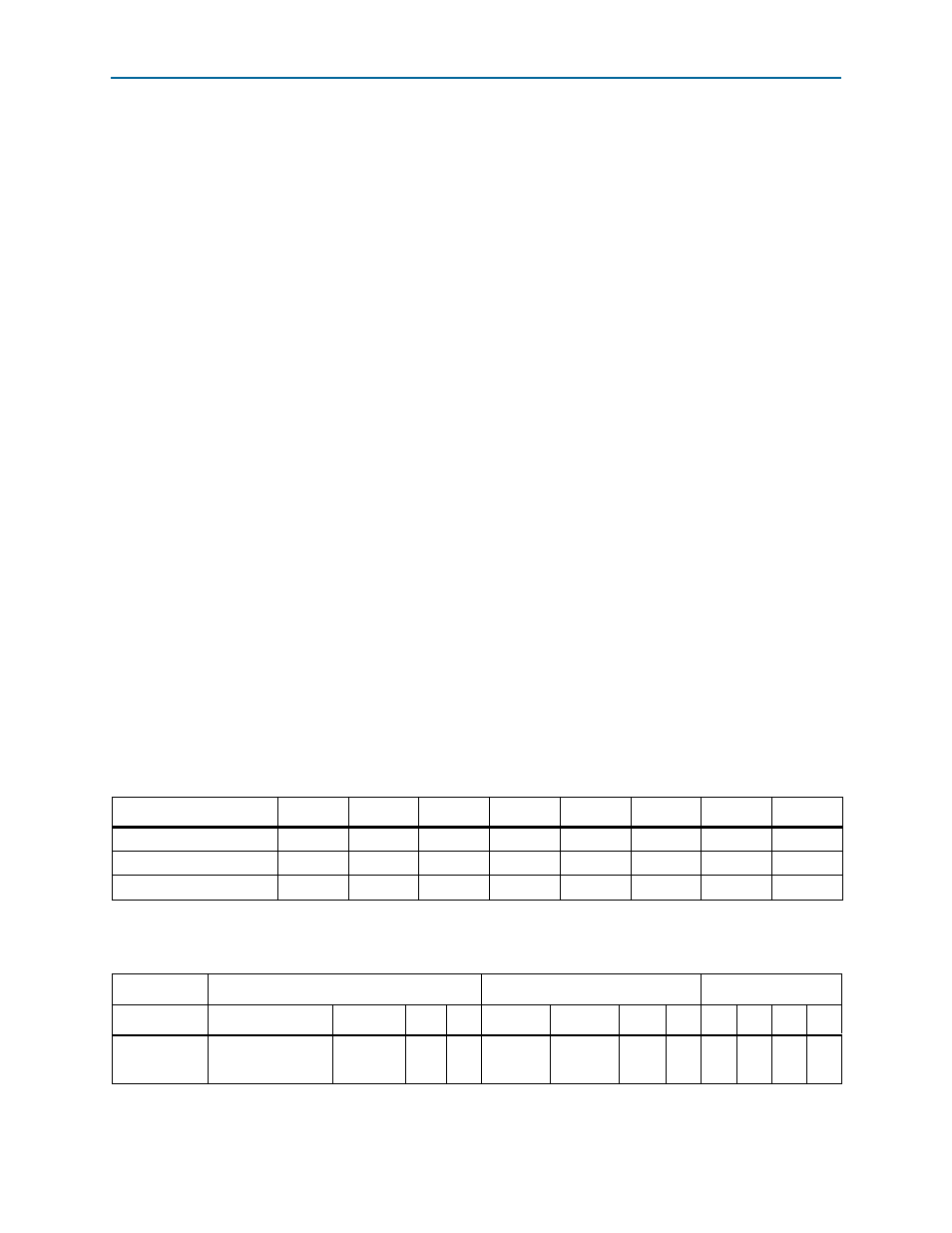

Table 9–4. Lane Assignments without Reversal

Lane Number

7

6

5

4

3

2

1

0

×8 IP core

7

6

5

4

3

2

1

0

×4 IP core

—

—

—

—

3

2

1

0

×1 IP core

—

—

—

—

—

—

—

0

Table 9–5. Lane Assignments with Reversal

Core Config

8

4

1

Slot Size

8

4

2

1

8

4

2

1

8

4

2

1

Lane

assignments

7:0,6:1,5:2,4:3,3:4,

2:5,1:6,0:7

3:4,2:5,

1:6,0:7

1:6,

0:7

0:7

7:0,6:1,

5:2,4:3

3:0,2:1,

1:2,0:3

3:0,

2:1

3:0

7:0

3:0

1:0

0:0