2, i3 – Altera IP Compiler for PCI Express User Manual

Page 15

Chapter 1: Datasheet

1–13

Recommended Speed Grades

August 2014

Altera Corporation

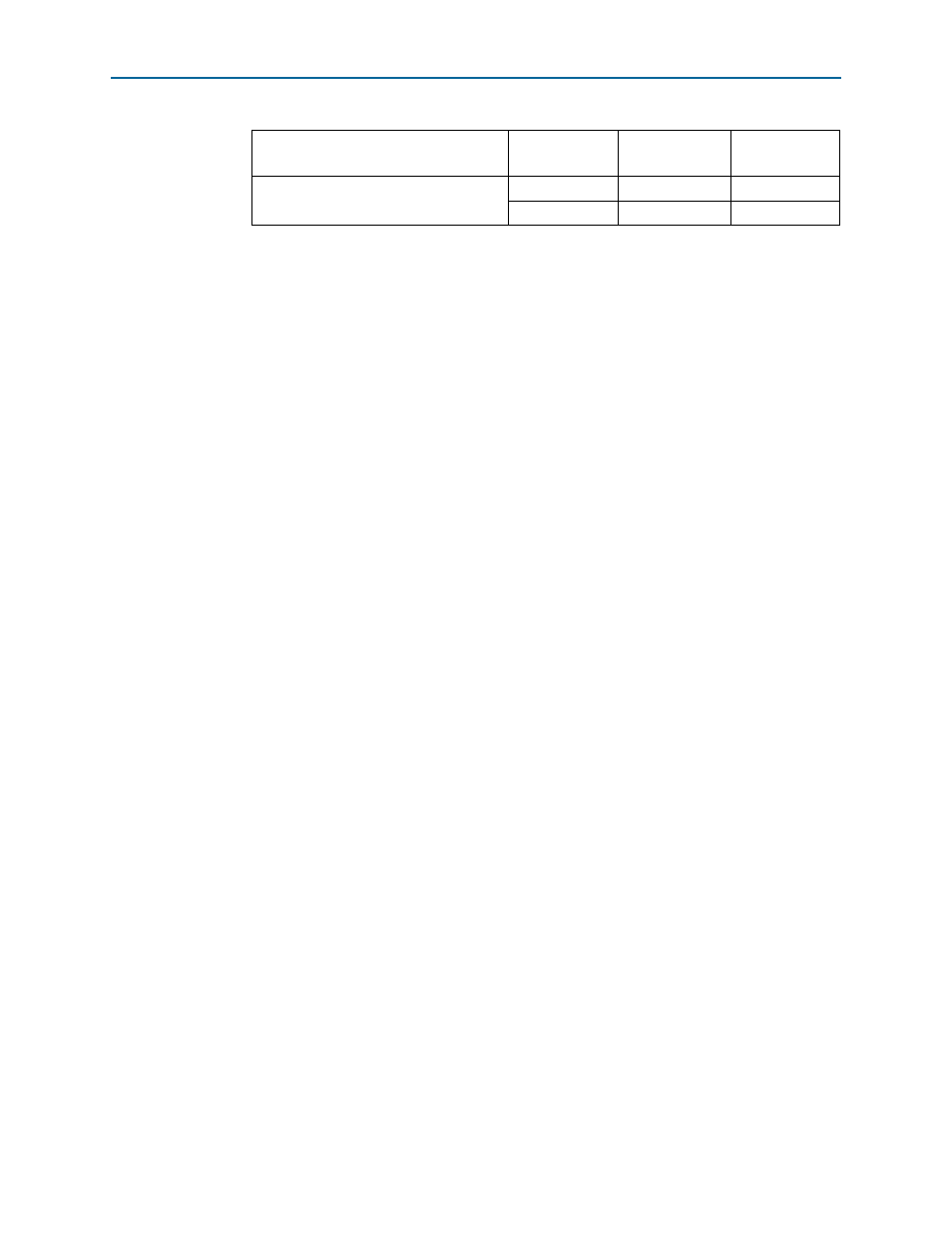

Stratix IV GX Gen1

×1

62.5

all speed grades

×4

125

all speed grades

Notes to

(1) The RX Buffer and Retry Buffer ECC options are only available in the hard IP implementation.

(2) This is a power-saving mode of operation.

(3) Final results pending characterization by Altera for speed grades -2, -3, and -4. Refer to the .fit.rpt file generated

by the Quartus II software.

(4) Closing timing for the –3 speed grades in the provided endpoint example design requires seed sweeping.

(5) You must turn on the following Physical Synthesis settings in the Quartus II Fitter Settings to achieve timing

closure for these speed grades and variations: Perform physical synthesis for combinational logic, Perform

register duplication, and Perform register retiming. In addition, you can use the Quartus II Design Space

Explorer or Quartus II seed sweeping methodology. Re

chapter in volume 2 of the Quartus II Handbook for more information about how to set these options.

(6) Altera recommends disabling the OpenCore Plus feature for the ×8 soft IP implementation because including this

feature makes it more difficult to close timing.

Table 1–9. Recommended Device Family Speed Grades (Part 2 of 2)

Device Family

Link Width

Internal Clock

Frequency (MHz)

Recommended

Speed Grades