Pci express megacore function, Tx slave module, Rx master module – Altera IP Compiler for PCI Express User Manual

Page 76: Pci express avalon-mm bridge, Pci link cra slave module

4–18

Chapter 4: IP Core Architecture

PCI Express Avalon-MM Bridge

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

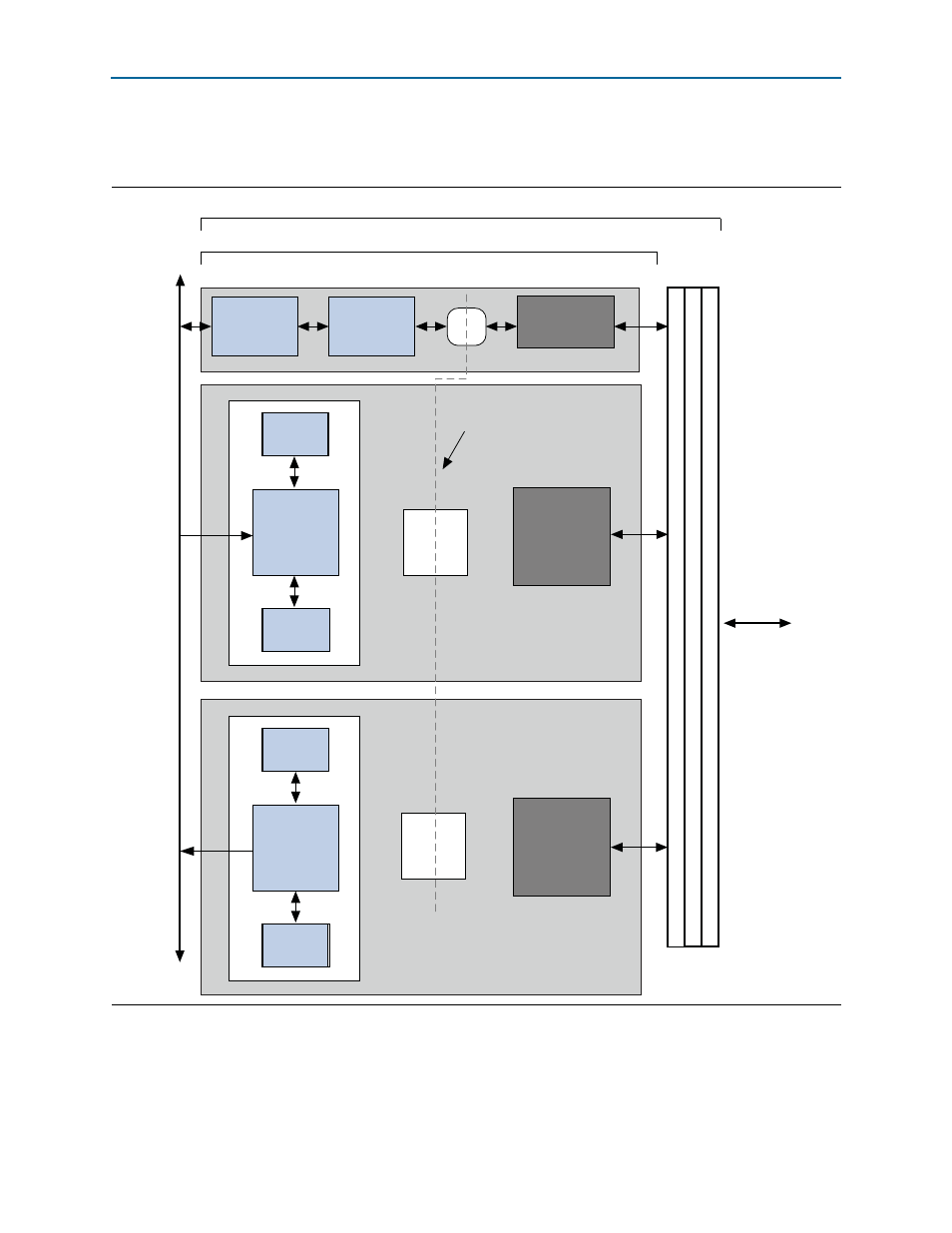

shows the block diagram of a full-featured PCI Express Avalon-MM

bridge.

The PCI Express Avalon-MM bridge supports the following TLPs:

■

Memory write requests

■

Received downstream memory read requests of up to 512 bytes in size

Figure 4–10. PCI Express Avalon-MM Bridge

Transaction Layer

PCI Express

Tx Controller

PCI Express

Rx Controller

Data Link Layer

Physical Layer

PCI Express MegaCore Function

Clock Domain

Boundary

Tx Slave Module

Control & Status

Reg (CSR)

Sync

Avalon Clock Domain

PCI Express Clock Domain

Rx Master Module

Rx Master Module

Clock

Domain

Crossing

Clock

Domain

Crossing

PCI Express Avalon-MM Bridge

System Interconnect Fabric

PCI Link

CRA Slave Module

Address

Translator

Avalon-MM

Tx Read

Response

Avalon-MM

Tx Slave

Address

Translator

Avalon-MM

Rx Read

Response

Avalon-MM

Rx Master

MSI or

Legacy Interrupt

Generator

Control Register

Access Slave