Altera IP Compiler for PCI Express User Manual

Page 199

Chapter 11: Flow Control

11–3

Throughput of Posted Writes

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

6. After an FC Update DLLP is created, it arbitrates for access to the PCI Express link.

The FC Update DLLPs are typically scheduled with a low priority; consequently, a

continuous stream of application layer TLPs or other DLLPs (such as ACKs) can

delay the FC Update DLLP for a long time. To prevent starving the attached

transmitter, FC Update DLLPs are raised to a high priority under the following

three circumstances:

a. When the last sent credit allocated counter minus the amount of received

data is less than MAX_PAYLOAD and the current credit allocated counter is

greater than the last sent credit counter. Essentially, this means the data sink

knows the data source has less than a full MAX_PAYLOAD worth of credits,

and therefore is starving.

b. When an internal timer expires from the time the last FC Update DLLP was

sent, which is configured to 30 µs to meet the

for

resending FC Update DLLPs.

c. When the credit allocated counter minus the last sent credit allocated

counter is greater than or equal to 25% of the total credits available in the RX

buffer, then the FC Update DLLP request is raised to high priority.

After arbitrating, the FC Update DLLP that won the arbitration to be the next item

is transmitted. In the worst case, the FC Update DLLP may need to wait for a

maximum sized TLP that is currently being transmitted to complete before it can

be sent.

7. The FC Update DLLP is received back at the original write requester and the

credit

limit value is updated. If packets are stalled waiting for credits, they can

now be transmitted.

To allow the write requester to transmit packets continuously, the credit allocated

and the credit limit counters must be initialized with sufficient credits to allow

multiple TLPs to be transmitted while waiting for the FC Update DLLP that

corresponds to the freeing of credits from the very first TLP transmitted.

shows the delay components for the FC Update Loop when the IP

Compiler for PCI Express is implemented in a Stratix II GX device. The delay

components are independent of the packet length. The total delays in the loop

increase with packet length.

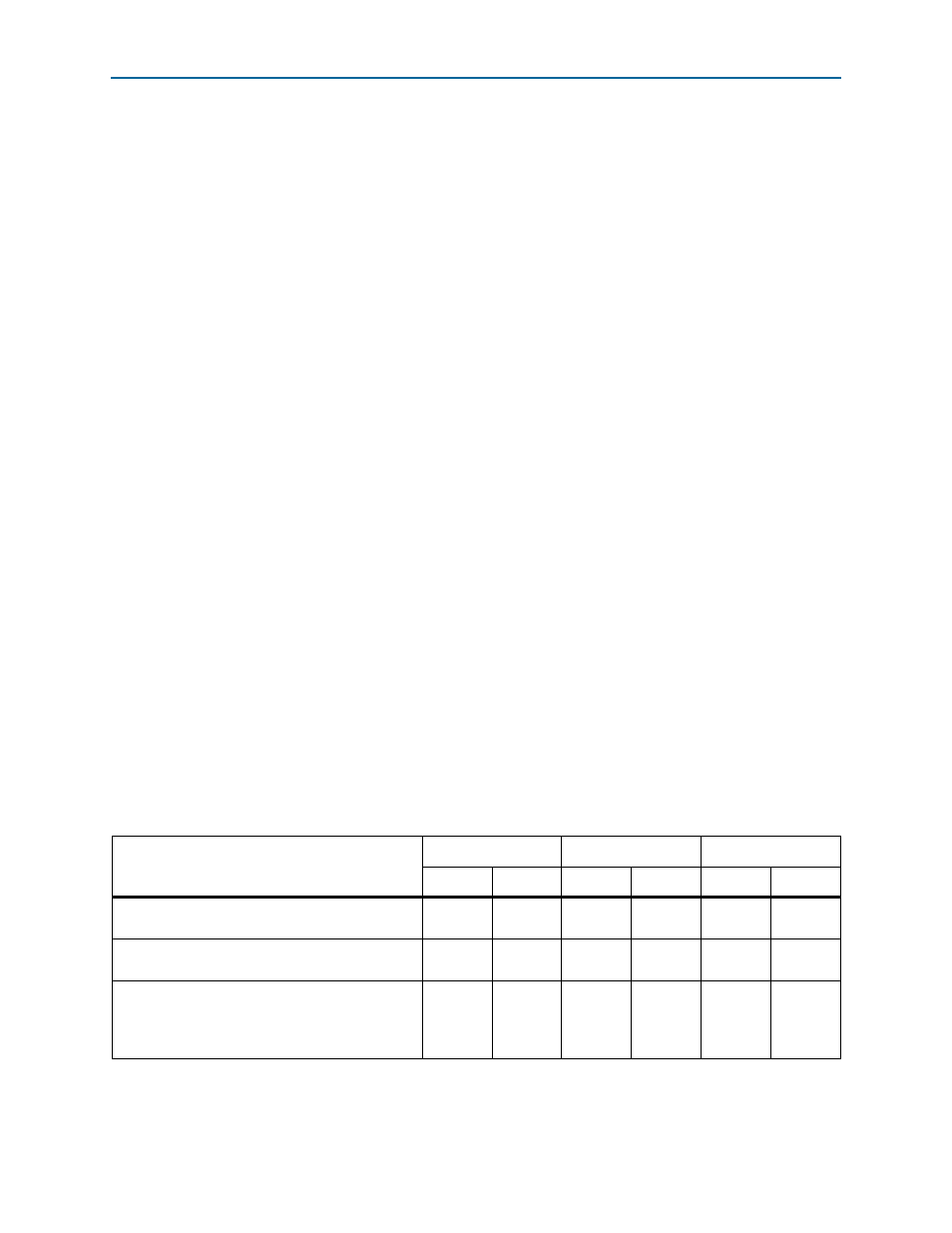

Table 11–1. FC Update Loop Delay in Nanoseconds Components For Stratix II GX (Part 1 of 2)

Delay Path

×8 Function

×4 Function

×1 Function

Min

Max

Min

Max

Min

Max

From decrement transmit credit consumed counter

to PCI Express Link.

60

68

104

120

272

288

From PCI Express Link until packet is available at

Application Layer interface.

124

168

200

248

488

536

From Application Layer draining packet to

generation and transmission of Flow Control (FC)

Update DLLP on PCI Express Link (assuming no

arbitration delay).

60

68

120

136

216

232