Altera IP Compiler for PCI Express User Manual

Page 112

5–26

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

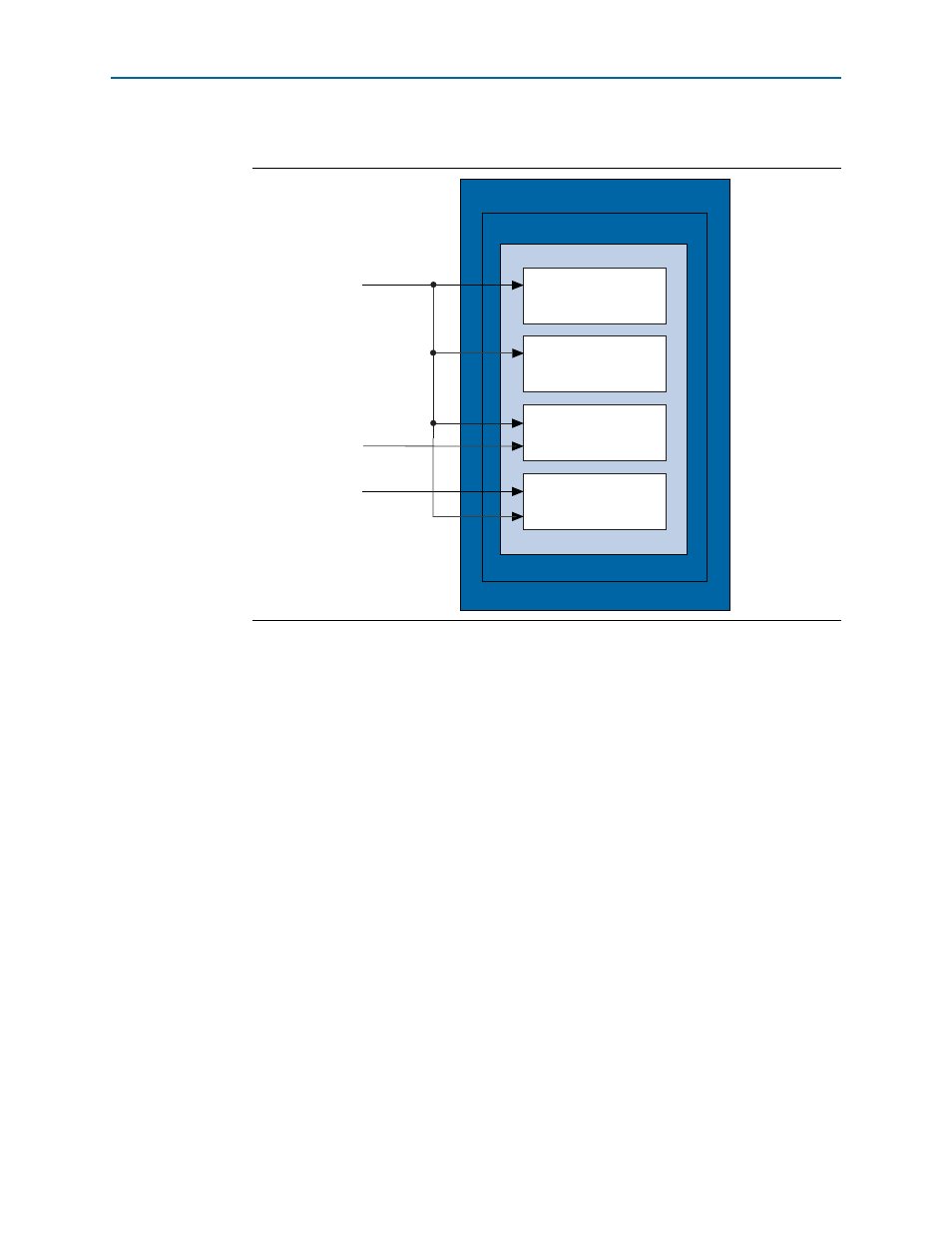

provides a simplified view of the logic controlled by the reset signals.

For root ports, srst should be asserted whenever l2_exit, hotrst_exit, dlup_exit,

and power-on-reset signals are asserted. The root port crst signal should be asserted

whenever l2_exit, hotrst_exit and other power-on-reset signals are asserted.

The IP Compiler for PCI Express soft IP implementation (×8) has two reset inputs,

npor

and rstn. The npor reset is used internally for all sticky registers that may not be

reset in L2 low power mode or by the fundamental reset. npor is typically generated

by a logical OR of the power-on-reset generator and the perst# signal from the

connector, as specified in the PCI Express Card Electromechanical Specification.

The

rstn signal is an asynchronous reset of the datapath state machines and the

nonsticky configuration space registers. Whenever the l2_exit, hotrst_exit,

dlup_exit

, or other power-on-reset signals are asserted, rstn should be asserted for

one or more cycles. When the perst# connector signal is asserted, rstn should be

asserted for a longer period of time to ensure that the root complex is stable and ready

for link training.

Figure 5–27. Reset Signal Domains

<variant>.v or .vhd

<variant>_core.v or .vhd

SERDES Reset

State Machine

Configuration Space

Sticky Registers

Datapath State Machines of

MegaCore Fucntion

Configuration Space

Non-Sticky Registers

srst

crst

altpcie_hip_pipen1b.v or .vhd

npor