Transaction layer not ready to accept packet – Altera IP Compiler for PCI Express User Manual

Page 336

B–18

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

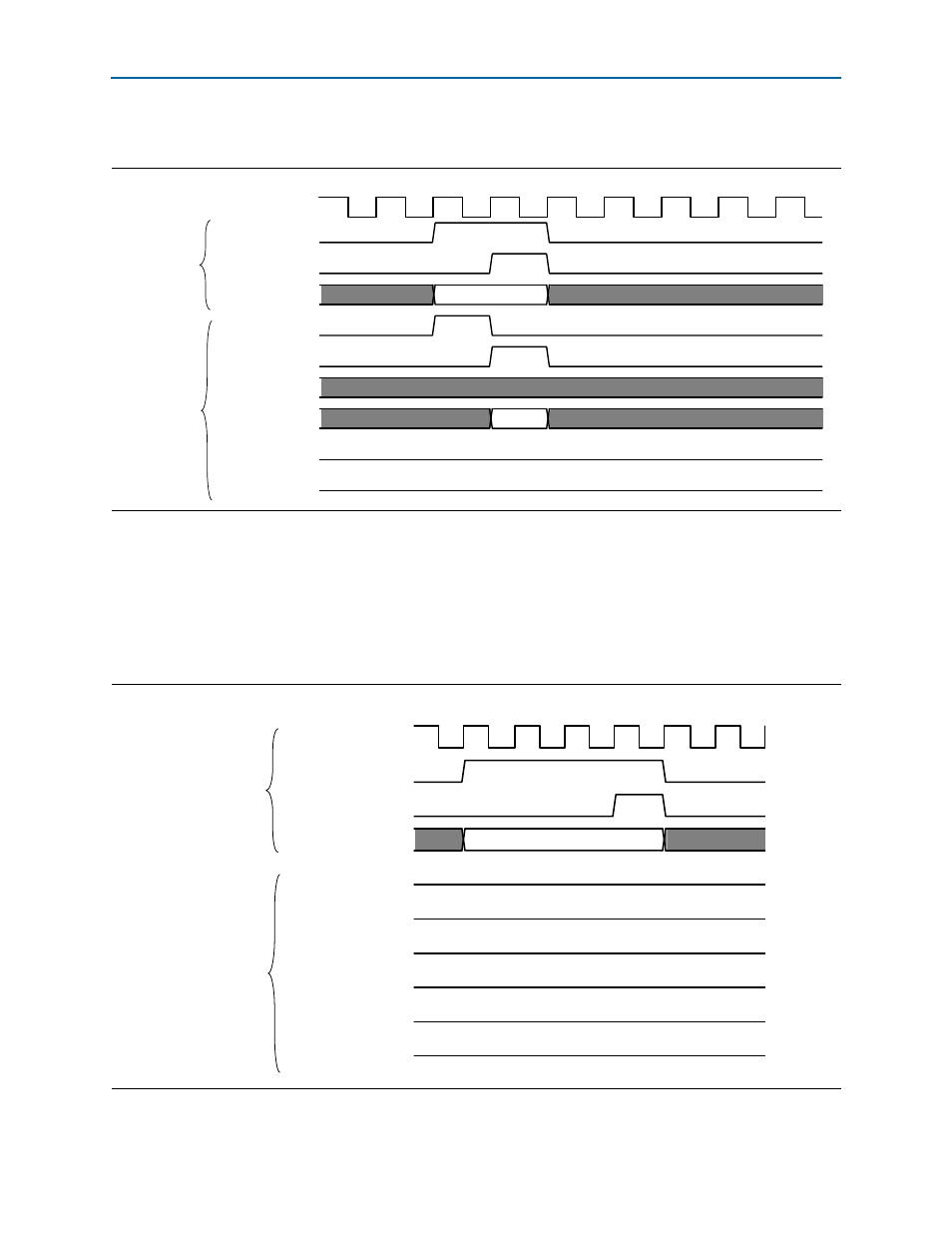

shows the IP core transmitting a memory write of one DWORD.

Transaction Layer Not Ready to Accept Packet

In this example, the application transmits a 64-bit memory read transaction of six

DWORDs. Address bit 2 is set to 0. Refer to

.

Data transmission cannot begin if the IP core’s transaction layer state machine is still

busy transmitting the previous packet, as is the case in this example.

Figure B–13. TX Transfer for A Single DWORD Write

clk

tx_req

tx_ack

tx_desc[127:0]

tx_dfr

tx_dv

tx_data[63:32]

tx_data[31:0]

tx_ws

tx_err

MEMWR32

DW0

Descriptor

Signals

Data

Signals

1

2

3

4

5

6

7

8

9

Figure B–14. TX State Machine Is Busy with the Preceding Transaction Layer Packet Waveform

clk

tx_req

tx_ack

tx_desc[127:0]

tx_dfr

tx_dv

tx_data[63:32]

tx_data[31:0]

tx_ws

tx_err

MEMWR64

1

2

3

4

5

6

7

Descriptor

Signals

Data

Signals