Altera IP Compiler for PCI Express User Manual

Page 340

B–22

Chapter :

Descriptor/Data Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

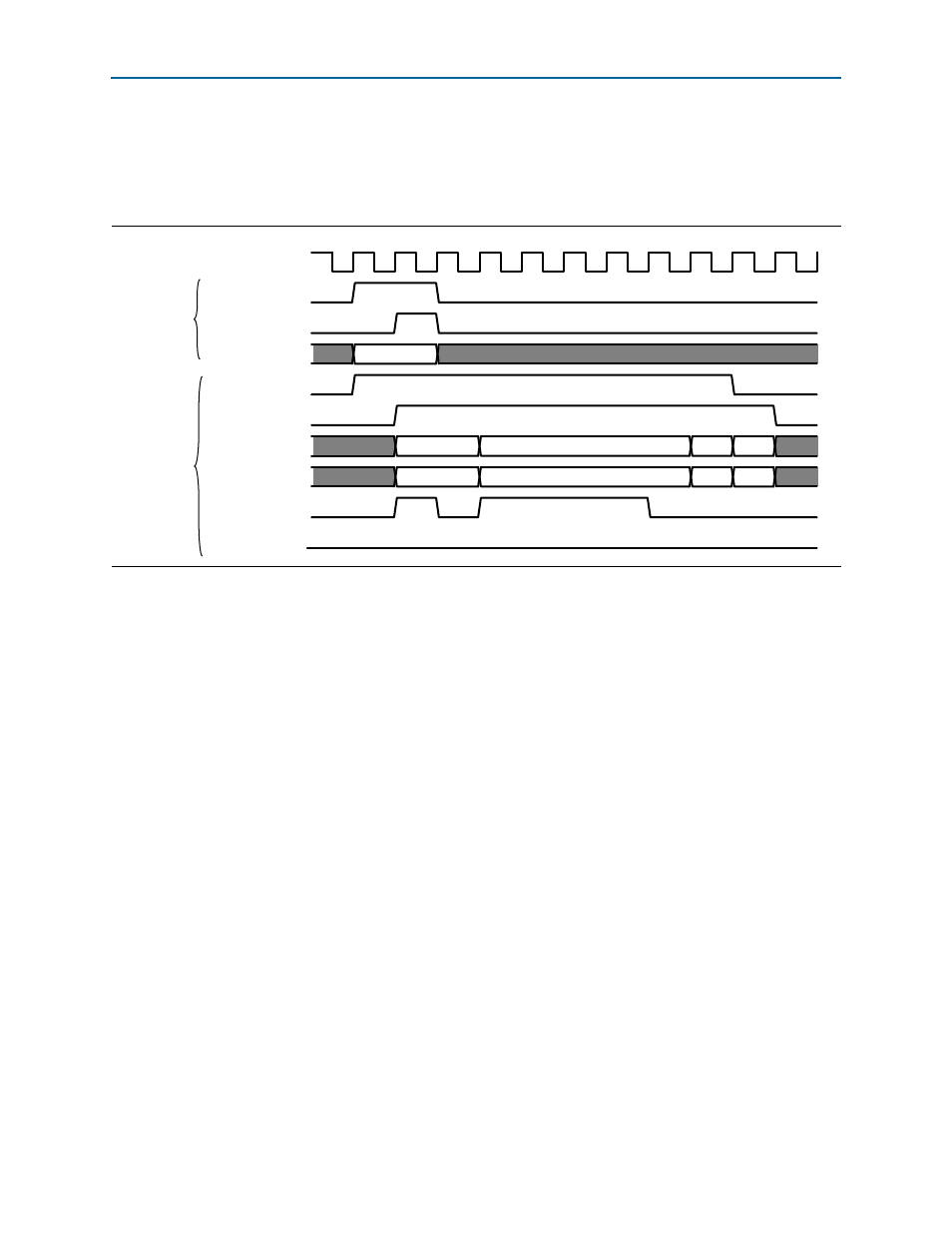

In clock cycle five, the IP core asserts tx_ws a second time to throttle the flow of data

because priority was not given immediately to this virtual channel. Priority was given

to either a pending data link layer packet, a configuration completion, or another

virtual channel. The tx_err is not available in the ×8 IP core.

Transmit Request Can Remain Asserted Between Transaction Layer Packets

In this example, the application transmits a 64-bit memory read transaction followed

by a 64-bit memory write transaction. Address bit 2 is set to 0. Refer to

In clock cycle four, tx_req is not deasserted between transaction layer packets.

Figure B–19. TX 64-Bit Memory Write Request Waveform

clk

tx_req

tx_ack

tx_desc[127:0]

tx_dfr

tx_dv

tx_data[63:32]

tx_data[31:0]

tx_ws

tx_err

MEMWR64

DW 1

DW 3

DW 5

DW 7

DW 0

DW 2

DW 4

DW 6

1

2

3

4

5

6

7

8

9

10

11

12

Descriptor

Signals

Data

Signals