Rx avalon-mm master signals – Altera IP Compiler for PCI Express User Manual

Page 135

Chapter 5: IP Core Interfaces

5–49

Avalon-MM Application Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

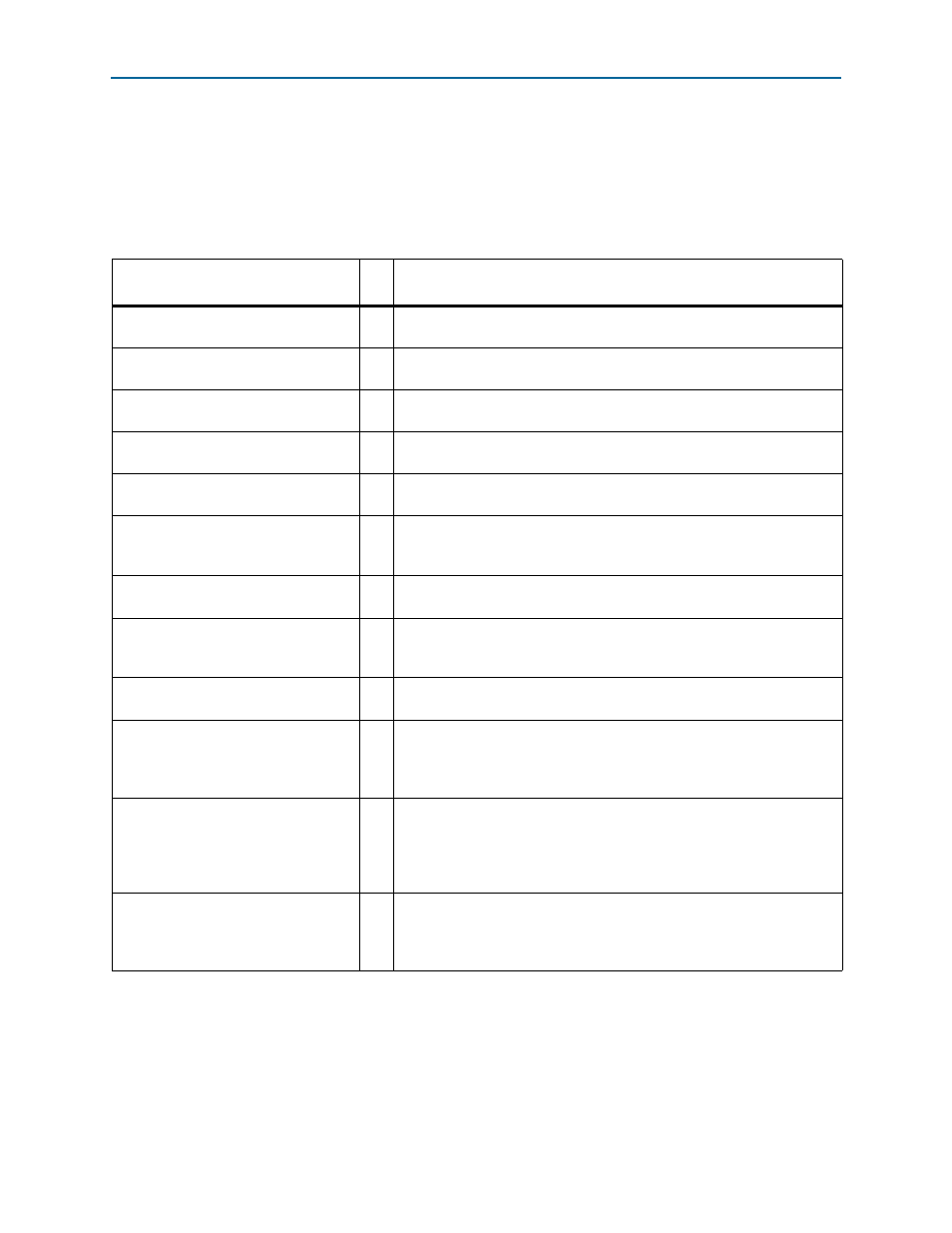

RX Avalon-MM Master Signals

This Avalon-MM master port propagates PCI Express requests to the Qsys

interconnect fabric. For the full-feature IP core it propagates requests as bursting reads

or writes. For the completer-only IP core, requests are a single dword.

lists

the RX Master interface ports.

Table 5–24. Avalon-MM RX Master Interface Signals

Signal Name in

Qsys

I/O

Description

RxmRead_o/

Bar<a>_<b>_read<n>

O

Asserted by the core to request a read.

RxmWrite_o/

Bar<a>_<b>_write<n>

O

Asserted by the core to request a write to an Avalon-MM slave.

RxmAddress_o[31:0]/

Bar<a>_<b>_address<n>[11:0]

O

The address of the Avalon-MM slave being accessed.

RxmWriteData_o[

<n>:0]/

Bar<a>_<b>_writedata<n>[63:0]

O

RX data being written to slave. <n> = 63 for the full-featured IP core. <n>

= 31 for the completer-only, single dword IP core.

RxmByteEnable_o[

<n>:0]/

Bar<a>_<b>_byteenable<n>[7:0]

O

Byte enable for write data. <n> = 63 for the full-featured IP core. <n> = 31

for the completer-only, single dword IP core.

RxmBurstCount_o[9:0]/

Bar<a>_<b>_burstcount<n>[6:0]

O

The burst count, measured in qwords, of the RX write or read request. The

width indicates the maximum data that can be requested. In Qsys

variations, the maximum data in a burst is 512 bytes.

RXmWaitRequest_i/

Bar<a>_<b>_waitrequest<n>

I

Asserted by the external Avalon-MM slave to hold data transfer.

RxmReadData_i[

<n>:0]/

Bar<a>_<b>_readdatavalid<n>

I

Read data returned from Avalon-MM slave in response to a read request.

This data is sent to the IP core through the TX interface. <n> = 7 for the

full-featured IP core. <n> = 3 for the completer-only, single dword IP core.

RxmReadDataValid_i/

Bar<a>_<b>_readdata<n>[63:0]

I

Asserted by the system interconnect fabric to indicate that the read data on

is valid.

RxmIrq_i/RxmIrq[

<n>:0]

I

Indicates an interrupt request asserted from the system interconnect fabric.

This signal is only available when the control register access port is

enabled. Qsys-generated variations have as many as 16 individual interrupt

signals (<n>

≤ 15).

RXmIrqNum_i[5:0]

/

not available in Qsys

I

Indicates the ID of the interrupt request being asserted. This signal is

available in completer only single dword variations without a control

register access port. This signal is not available in Qsys-generated

variations, because the Qsys variations implement the Avalon-MM

individual requests interrupt scheme.

RxmResetRequest_o/

not available in

Qsys

O

This reset signal is asserted if any of the following conditions are true:

npor

, l2_exit, hotrst_exist, dlup_exit, or reset_n are asserted, or

ltssm == 5’h10

. Refer to

the reset logic when using the IP Compiler for PCI Express.