External phy support, Debug features, Ip core verification – Altera IP Compiler for PCI Express User Manual

Page 11: Of 2), Note 1)

Chapter 1: Datasheet

1–9

IP Core Verification

August 2014

Altera Corporation

1

The device names and part numbers for Altera FPGAs that include internal

transceivers always include the letters GX, GT, or GZ. If you select a device that does

not include an internal transceiver, you can use the PIPE interface to connect to an

external PHY.

lists the available external PHY types.

You can customize the payload size, buffer sizes, and configuration space (base

address registers support and other registers). Additionally, the IP Compiler for PCI

Express supports end-to-end cyclic redundancy code (ECRC) and advanced error

reporting for ×1, ×2, ×4, and ×8 configurations.

External PHY Support

Altera IP Compiler for PCI Express variations support a wide range of PHYs,

including the TI XIO1100 PHY in 8-bit DDR/SDR mode or 16-bit SDR mode; NXP

PX1011A for 8-bit SDR mode, a serial PHY, and a range of custom PHYs using

8-bit/16-bit SDR with or without source synchronous transmit clock modes and 8-bit

DDR with or without source synchronous transmit clock modes. You can constrain TX

I/Os by turning on the Fast Output Enable Register option in the parameter editor,

or by editing this setting in the Quartus II Settings File (.qsf). This constraint ensures

fastest t

CO

timing.

Debug Features

The IP Compiler for PCI Express also includes debug features that allow observation

and control of the IP cores for faster debugging of system-level problems.

f

For more information about debugging refer to

IP Core Verification

To ensure compliance with the PCI Express specification, Altera performs extensive

validation of the IP Compiler for PCI Express. Validation includes both simulation

and hardware testing.

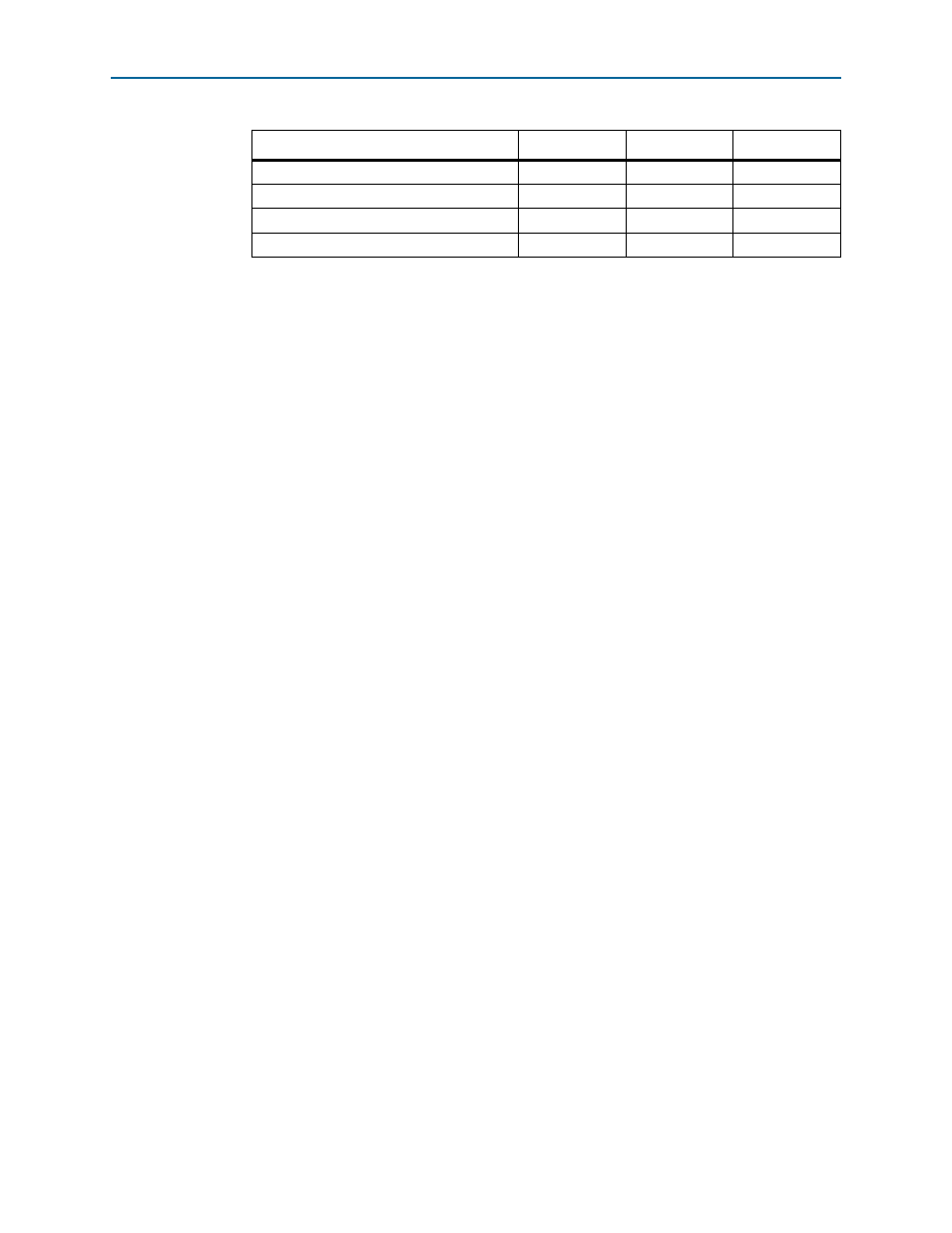

Arria II GX–Gen1 Hard IP Implementation

Yes

Yes

Yes

Arria II GX–Gen1 Soft IP Implementation

Yes

Yes

No

Arria II GZ–Gen1 Hard IP Implementation

Yes

Yes

Yes

Arria II GZ–Gen2 Hard IP Implementation

Yes

Yes

No

Notes to

(1) Refer to

for a list of features available in the different implementations and design flows.

(2) Not available in -4 speed grade. Requires -2 or -3 speed grade.

(3) Gen2 ×8 is only available in the -2 and I3 speed grades.

Table 1–7. Operation in Devices with HSSI Transceivers (Part 2 of 2)

(Note 1)

Device Family

×1

×4

×8