Altera IP Compiler for PCI Express User Manual

Page 57

Chapter 3: Parameter Settings

3–21

IP Core Parameters

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

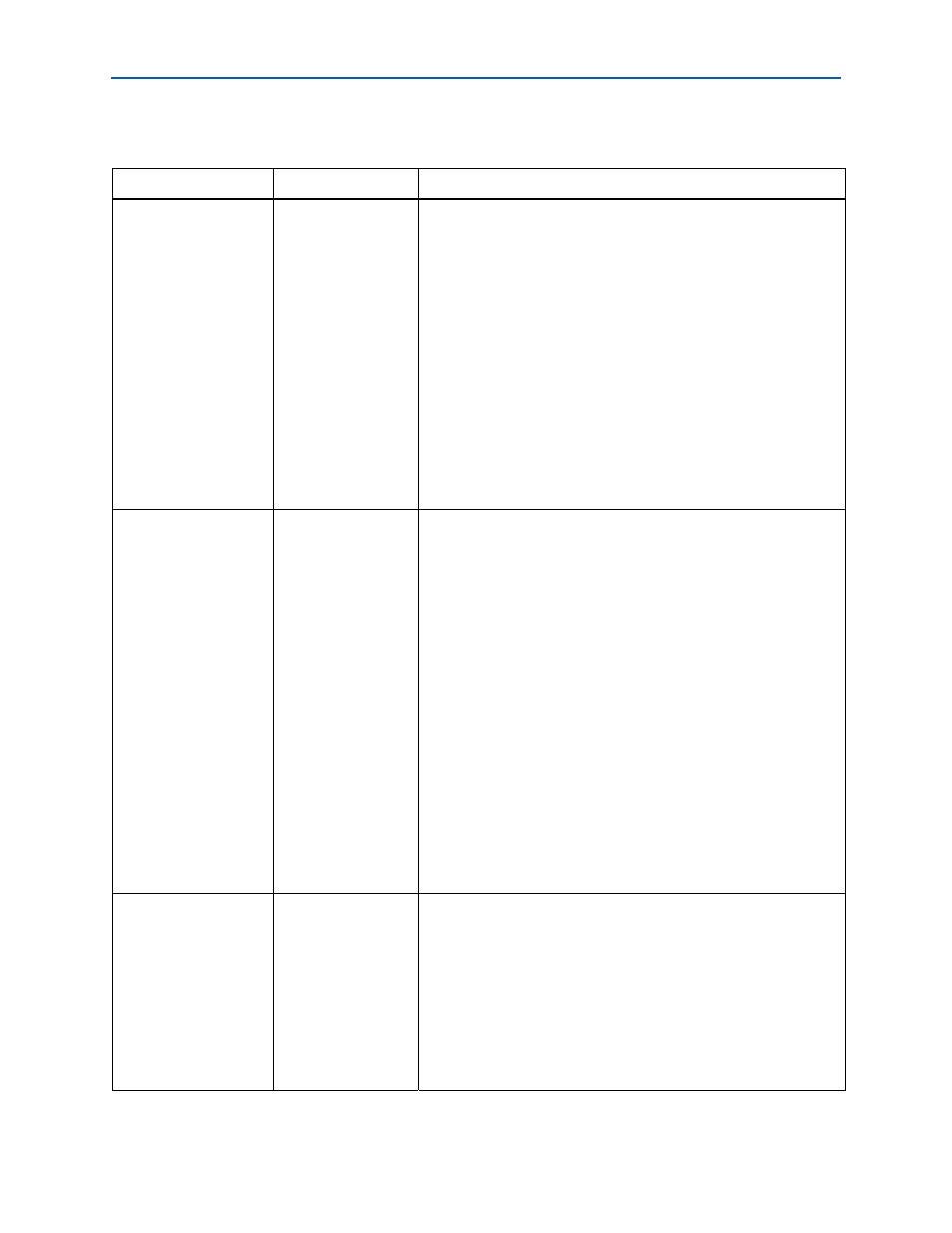

Table 3–14. Avalon Configuration Settings (Part 1 of 2)

Parameter Value

Description

Avalon Clock Domain

Use PCIe core clock

Use separate clock

Allows you to specify one or two clock domains for your application

and the IP Compiler for PCI Express. The single clock domain is higher

performance because it avoids the clock crossing logic that separate

clock domains require.

Use PCIe core clock—In this mode, the IP Compiler for PCI Express

provides a clock output, clk125_out or pcie_clk_out, to be used

as the single clock for the IP Compiler for PCI Express and the

system application clock.

Use separate clock—In this mode, the protocol layers of the IP

Compiler for PCI Express operate on an internally generated clock.

The IP Compiler for PCI Express exports clk125_out; however, this

clock is not visible and cannot drive the components. The Avalon-

MM bridge logic of the IP Compiler for PCI Express operates on a

different clock.

For more information about these two modes, refer to

Interface–Hard IP and Soft IP Implementations” on page 7–11

PCIe Peripheral Mode

Requester/Completer,

Completer-Only,

Completer-Only

single dword

Specifies whether the IP Compiler for PCI Express component is

capable of sending requests to the upstream PCI Express devices, and

whether the incoming requests are pipelined.

Requester/Completer—Enables the IP Compiler for PCI Express to

send request packets on the PCI Express TX link as well as receiving

request packets on the PCI Express RX link.

Completer-Only—In this mode, the IP Compiler for PCI Express can

receive requests, but cannot initiate upstream requests. However, it

can transmit completion packets on the PCI Express TX link. This

mode removes the Avalon-MM TX slave port and thereby reduces

logic utilization. When selecting this option, you should also select

Low for the Desired performance for received completions option

on the Buffer Setup page to minimize the device resources

consumed. Completer-Only is only available in hard IP

implementations.

Completer-Only single dword—Non-pipelined version of

Completer-Only mode. At any time, only a single request can be

outstanding. Completer-Only single dword uses fewer resources

than Completer-Only and is only available in hard IP

implementations.

Address translation

table configuration

Dynamic translation

table,

Fixed translation

table

Sets Avalon-MM-to-PCI Express address translation scheme to

dynamic or fixed.

Dynamic translation table—Enables application software to write

the address translation table contents using the control register

access slave port. On-chip memory stores the table. Requires that

the Avalon-MM CRA Port be enabled. Use several address

translation table entries to avoid updating a table entry before

outstanding requests complete.

Fixed translation table—Configures the address translation table

contents to hardwired fixed values at the time of system generation.