Transaction layer routing rules, Note 1) – Altera IP Compiler for PCI Express User Manual

Page 179

Chapter 8: Transaction Layer Protocol (TLP) Details

8–3

Transaction Layer Routing Rules

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Transaction Layer Routing Rules

Transactions adhere to the following routing rules:

■

In the receive direction (from the PCI Express link), memory and I/O requests that

match the defined base address register (BAR) contents and vendor-defined

messages with or without data route to the receive interface. The application layer

logic processes the requests and generates the read completions, if needed.

■

In endpoint mode, received type 0 configuration requests from the PCI Express

upstream port route to the internal configuration space and the IP core generates

and transmits the completion.

■

In root port mode, the application can issue type 0 or type 1 configuration TLPs on

the Avalon-ST TX bus.

■

The type 1 configuration TLPs are sent downstream on the PCI Express link

toward the endpoint that matches the completer ID set in the transmit packet.

If the bus number of the type 1 configuration TLP matches the Subordinate Bus

Number register value in the root port configuration space, the TLP is

converted to a type 0 TLP.

■

The type 0 configuration TLPs are only routed to the configuration space of the

IP core configured as a root port and are not sent downstream on the PCI

Express link.

■

The IP core handles supported received message transactions (power management

and slot power limit) internally.

■

Vendor defined message TLPs are passed to the application layer.

■

The transaction layer treats all other received transactions (including memory or

I/O requests that do not match a defined BAR) as unsupported requests. The

transaction layer sets the appropriate error bits and transmits a completion, if

needed. These unsupported requests are not made visible to the application layer,

the header and data is dropped.

■

For memory read and write request with addresses below 4 GBytes, requestors

must use the 32-bit format. The transaction layer interprets requests using the

64-bit format for addresses below 4 GBytes as malformed packets and does not

send them to the application layer. If the AER option is on, an error message TLP is

sent to the root port.

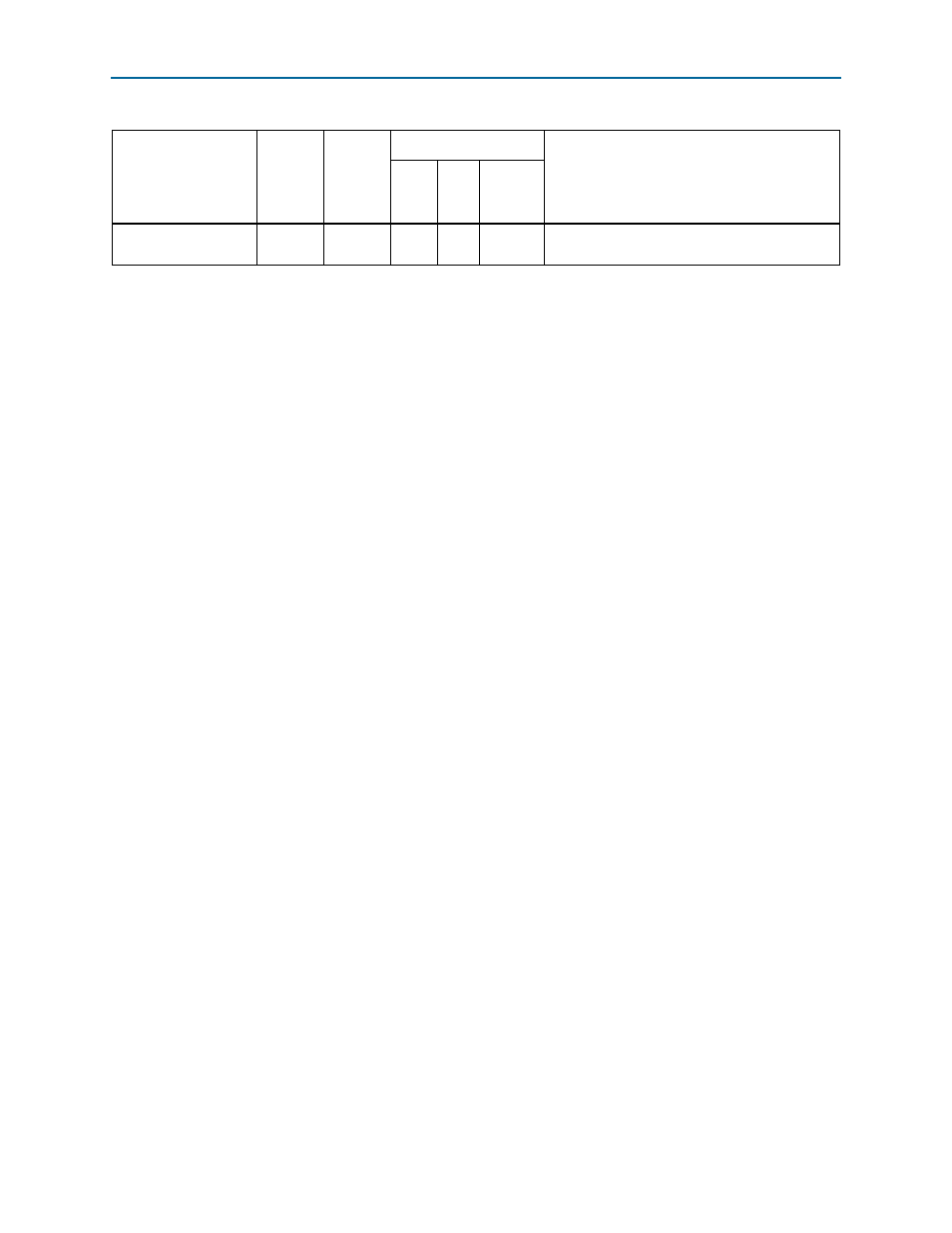

Attention

Button_Pressed

Receive

Transmit

No

No

Yes

Notes to

(1) In the

2.0

, this message is no longer mandatory after link training.

(2) In endpoint mode.

Table 8–1. Supported Message Types (Part 3 of 3)

(Note 1)

Message

Root

Port

Endpoint

Generated by

Comments

App

Layer

Core

Core

(with AL

input)