Altera IP Compiler for PCI Express User Manual

Page 262

15–30

Chapter 15: Testbench and Design Example

Root Port BFM

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

The ebfm_cfg_rp_ep procedure also sets up a bar_table data structure in BFM shared

memory that lists the sizes and assigned addresses of all endpoint BARs. This area of

BFM shared memory is write-protected, which means any user write accesses to this

area cause a fatal simulation error. This data structure is then used by subsequent

BFM procedure calls to generate the full PCI Express addresses for read and write

requests to particular offsets from a BAR. This procedure allows the testbench code

that accesses the endpoint application layer to be written to use offsets from a BAR

and not have to keep track of the specific addresses assigned to the BAR.

shows how those offsets are used.

The configuration routine does not configure any advanced PCI Express capabilities

such as the virtual channel capability or advanced error reporting capability.

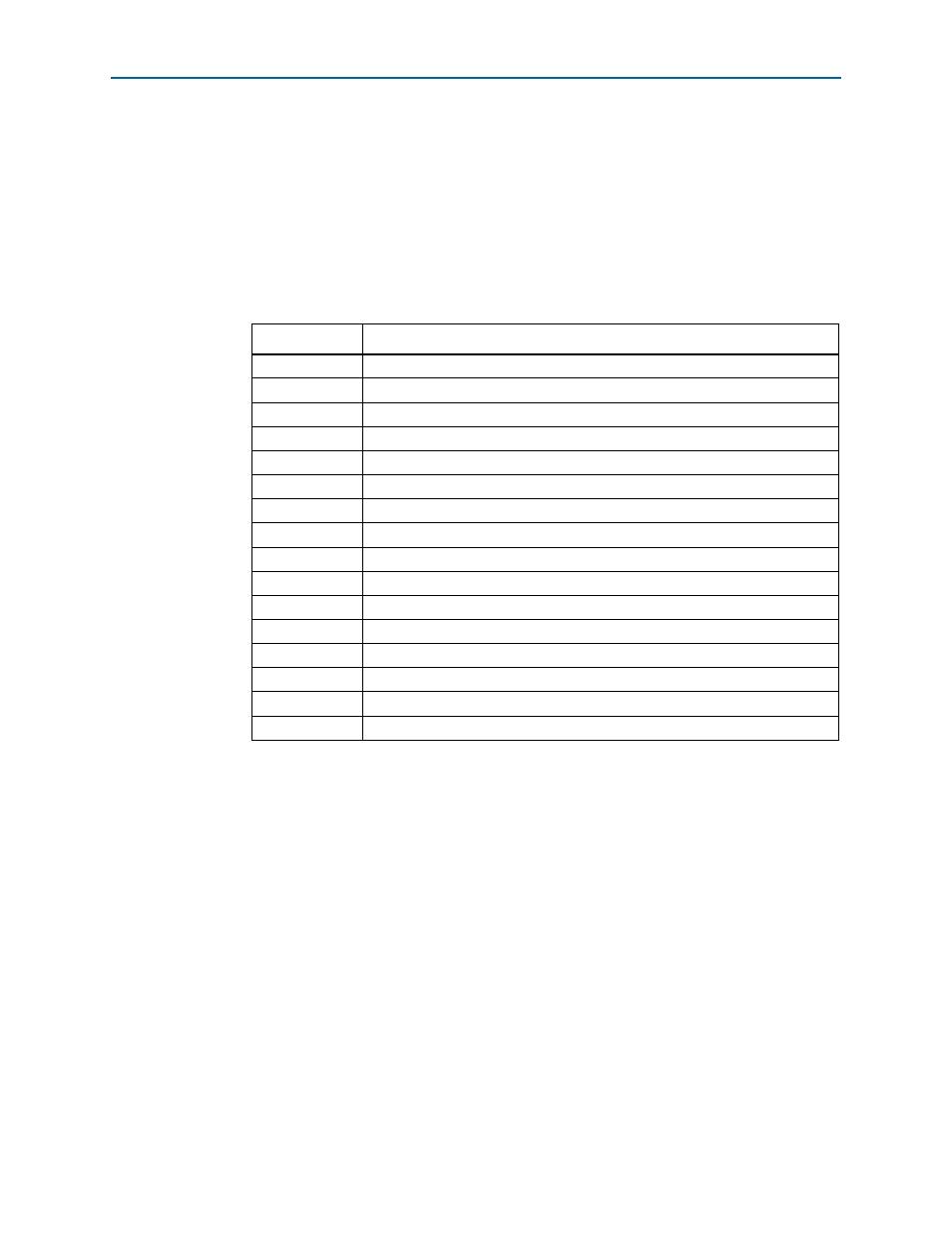

Table 15–22. BAR Table Structure

Offset (Bytes)

Description

+0

PCI Express address in BAR0

+4

PCI Express address in BAR1

+8

PCI Express address in BAR2

+12

PCI Express address in BAR3

+16

PCI Express address in BAR4

+20

PCI Express address in BAR5

+24

PCI Express address in Expansion ROM BAR

+28

Reserved

+32

BAR0 read back value after being written with all 1’s (used to compute size)

+36

BAR1 read back value after being written with all 1’s

+40

BAR2 read back value after being written with all 1’s

+44

BAR3 read back value after being written with all 1’s

+48

BAR4 read back value after being written with all 1’s

+52

BAR5 read back value after being written with all 1’s

+56

Expansion ROM BAR read back value after being written with all 1’s

+60

Reserved