Altera IP Compiler for PCI Express User Manual

Page 343

Chapter :

B–25

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

Completion Interface Signals for Descriptor/Data Interface

describes the signals that comprise the completion interface for the

descriptor/data interface.

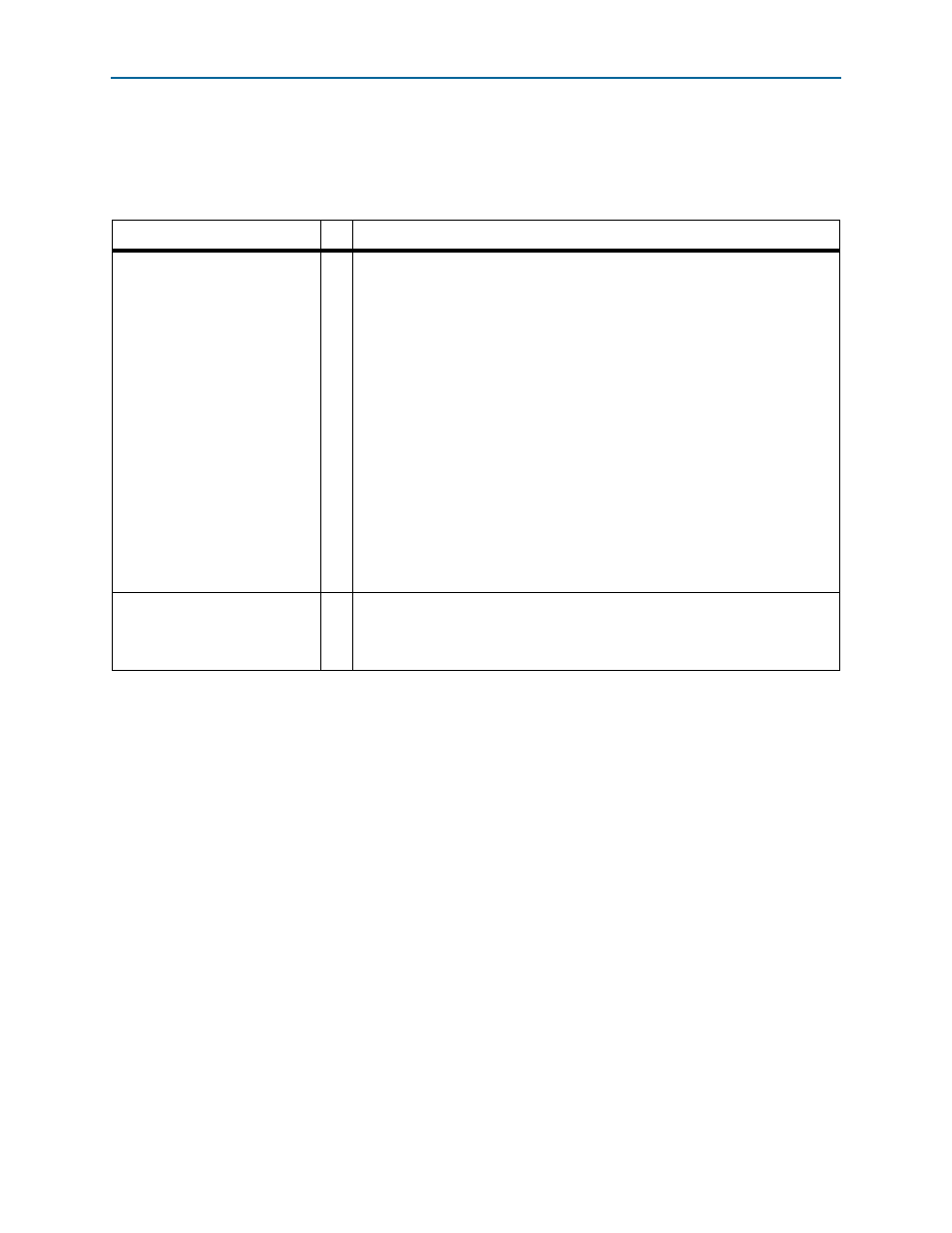

Table B–11. Completion Interface Signals

Signal

I/O

Description

cpl_err[2:0]

I

Completion error. This signal reports completion errors to the configuration space

by pulsing for one cycle. The three types of errors that the application layer must

report are:

■

cpl_err[0]

: Completion timeout error. This signal must be asserted when a

master-like interface has performed a non-posted request that never receives a

corresponding completion transaction after the 50 ms time-out period. The IP

core automatically generates an error message that is sent to the root complex.

■

cpl_err[1]

: Completer abort error. This signal must be asserted when a

target block cannot process a non-posted request. In this case, the target block

generates and sends a completion packet with completer abort (CA) status to

the requestor and then asserts this error signal to the IP core. The block

automatically generates the error message and sends it to the root complex.

■

cpl_err[2]

: Unexpected completion error. This signal must be asserted when

a master block detects an unexpected completion transaction, for example, if

no completion resource is waiting for a specific packet.

For ×1 and ×4 the wrapper output is a 7-bit signal with the following format:

{3’h0, cpl_err[2:0], 1’b0}

cpl_pending

I

Completion pending. The application layer must assert this signal when a master

block is waiting for completion, for example, when a transaction is pending. If this

signal is asserted and low power mode is requested, the IP core waits for the

deassertion of this signal before transitioning into low-power state.