R to, Figure 7–1 – Altera IP Compiler for PCI Express User Manual

Page 166

7–2

Chapter 7: Reset and Clocks

Reset Hard IP Implementation

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

■

test_in

settings

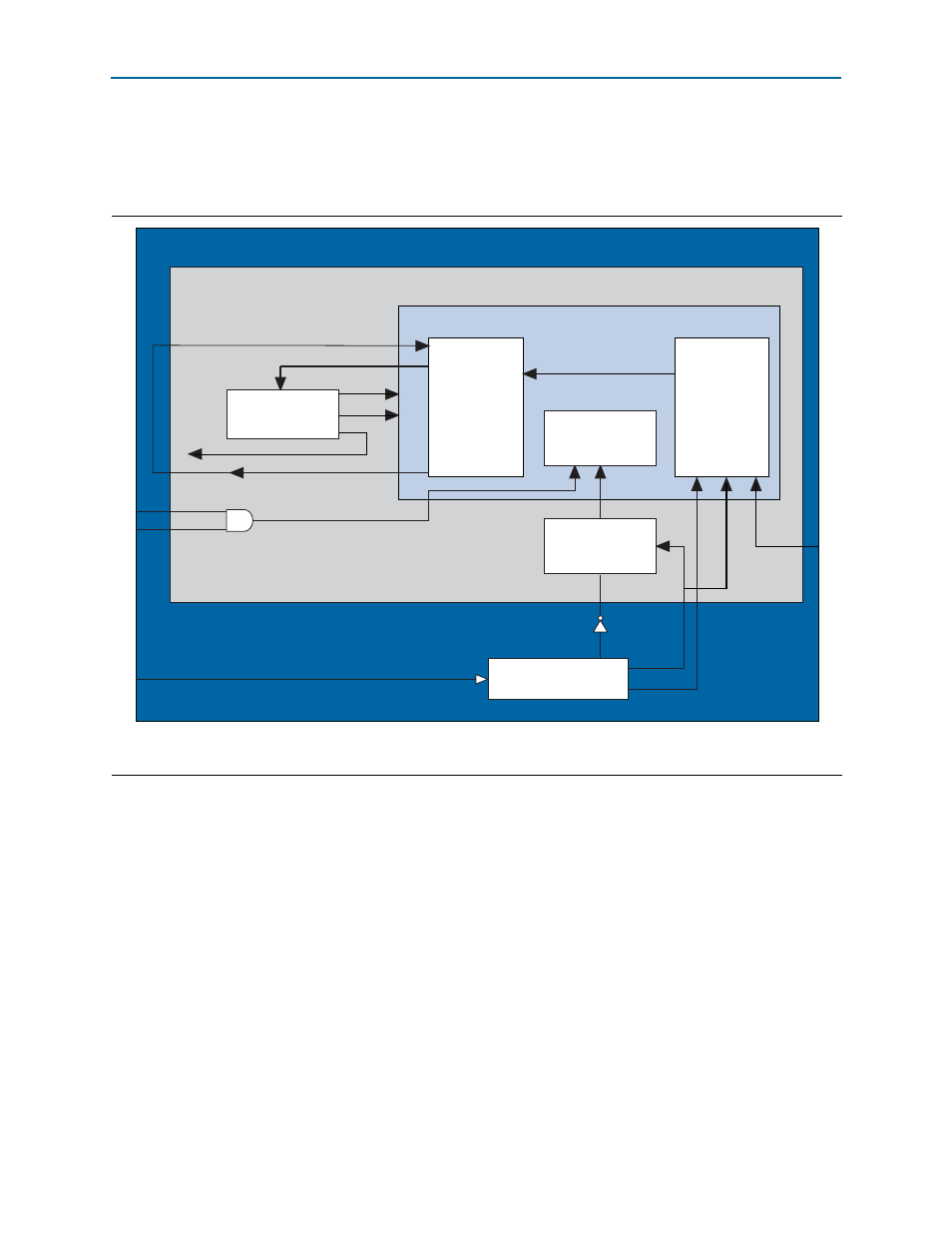

illustrates the reset logic for both the <variant>_plus.v or .vhd and

<variant>.v or .vhd options.

In

, a general purpose PLL receives a free running clock source which is

independent of the transceiver reference clock refclk, and outputs a 125 MHz

fixedclk

and a reconfig_clk. The altgxb_reconfig block waits until the two PLL

output clocks are stable before running offset cancellation. The pll_locked signal

indicates whether the two clocks are stable. The fixedclk_serdes input to the

transceiver must be a free running clock; the block diagram shows that the fixedclk is

free running, because it is derived from a free running input clock by an independent

PLL. The altgxb_reconfig block outputs a busy signal that connects to the

busy_altgxb_reconfig

input port of the IP Compiler for PCI Express transceiver reset

controller. After offset cancellation completes, ALTGXB_Reconfig deasserts the busy

signal. The reset controller waits for the first falling edge of this signal.

The inverse of the pll_locked signal is the offset_cancellation_reset signal. The

signal is not labeled in

because it is not visible outside the IP Compiler for

PCI Express. However, you can make the offset_cancellation_reset signal visible

using the following command:

Figure 7–1. Internal Reset Modules in the Hard IP Implementation

Note to

(1) Refer to

for more detail on this variant.

IP Compiler for PCI Express Hard IP Implementation with Reset and Calibration Logic Included

crst

dl_up, hotrst_exit,

l2_exit, ltssm

app_rstn

coreclk_out 125 MHz

pld_clk 125 MHz

srst

busy_altgxb_reconfig

<variant>_example_chaining_pipen1b.v or .vhd

Transceiver

PHY IP Core

<variant>.v or .vhd

<variant>_plus.v or .vhd

<variant>_serdes.v

or .vhd

IP Compiler

for PCI Express

Hard IP

Implementation

<variant>_core.v

or .vhd

Hip_txclk 250 or 500 MHz

Transceiver Reset

altpcie_rs_serdes.v

or .vhd

altpcie_reconfig_

<device>.v or .vhd

altgxb_reconfig

altpcierd_reconfig_pll_clk.v

free_running_clock 100 MHz

Refclk

100 MHz

cal_blk_clk

50 MHz

pll_locked

fixedclk

fixedclk_serdes

reconfig_clk

125 MHz

50 MHz

Transceiver Reset

<variant>_rs_hip.v

or .vhd

PLL

pcie_rstn

Note (1)

local_rstn