Bfm log and message procedures, Log constants, Bfm log and – Altera IP Compiler for PCI Express User Manual

Page 275: For more in

Chapter 15: Testbench and Design Example

15–43

BFM Procedures and Functions

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

BFM Log and Message Procedures

The following procedures and functions are available in the VHDL package file

altpcietb_bfm_log.vhd

or in the Verilog HDL include file altpcietb_bfm_log.v that

uses the altpcietb_bfm_log_common.v module, instantiated at the top level of the

testbench.

These procedures provide support for displaying messages in a common format,

suppressing informational messages, and stopping simulation on specific message

types.

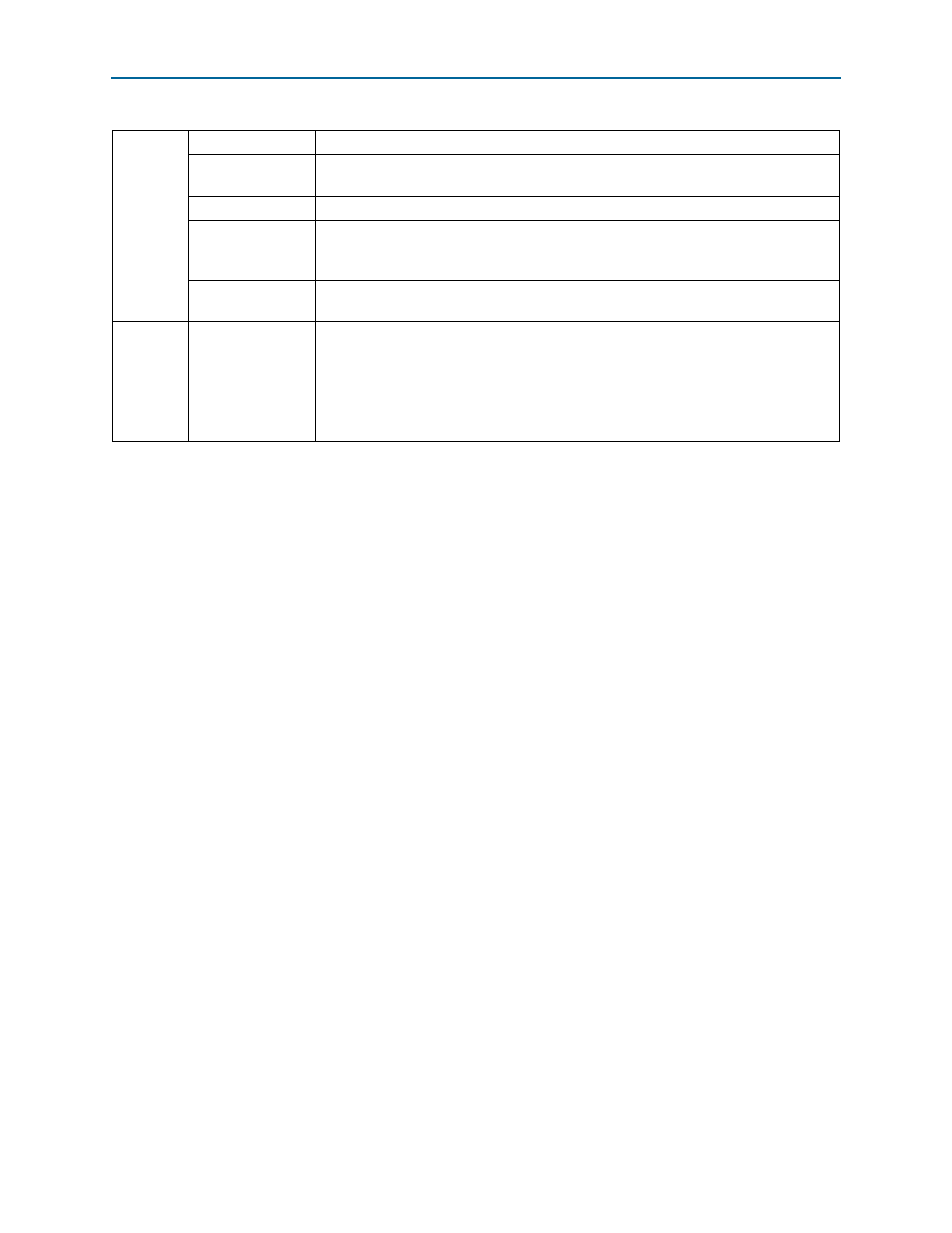

Log Constants

The following constants are defined in the BFM Log package. They define the type of

message and their values determine whether a message is displayed or simulation is

stopped after a specific message. Each displayed message has a specific prefix, based

on the message type in

.

You can suppress the display of certain message types. The default values

determining whether a message type is displayed are defined in

. To

change the default message display, modify the display default value with a

procedure call to ebfm_log_set_suppressed_msg_mask.

Certain message types also stop simulation after the message is displayed.

shows the default value determining whether a message type stops

simulation. You can specify whether simulation stops for particular messages with the

procedure ebfm_log_set_stop_on_msg_mask.

Arguments

addr

BFM shared memory starting address for checking data.

mode

Data pattern used for checking the data. Should be one of the constants defined in

section

“Shared Memory Constants” on page 15–41

leng

Length, in bytes, of data to check.

init

In VHDL. this argument is type std_logic_vector(63 downto 0). In Verilog HDL,

this argument is reg [63:0].In both languages, the necessary least significant bits are

used for the data patterns that are smaller than 64-bits.

display_error

When set to 1, this argument displays the mis-comparing data on the simulator standard

output.

Return

Result

Result is VHDL type Boolean.

TRUE—Data pattern compared successfully

FALSE—Data pattern did not compare successfully

Result in Verilog HDL is 1-bit.

1’b1 — Data patterns compared successfully

1’b0 — Data patterns did not compare successfully

Table 15–38. shmem_chk_ok Function (Part 2 of 2)