Table b–3 – Altera IP Compiler for PCI Express User Manual

Page 323

Chapter :

B–5

Descriptor/Data Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

The IP core generates the eight MSBs of this signal with BAR decoding information.

Refer to

.

describes the data phase signals.

rx_mask<n>

I

Receive mask (non-posted requests). This signal is used to mask all non-posted

request transactions made to the application interface to present only posted and

completion transactions. This signal must be asserted with rx_retry<n> and

deasserted when the IP core can once again accept non-posted requests.

Note to

(1) For all signals, <n> is the virtual channel number which can be 0 or 1.

Table B–2. RX Descriptor Phase Signals (Part 2 of 2)

Signal

I/O

Description

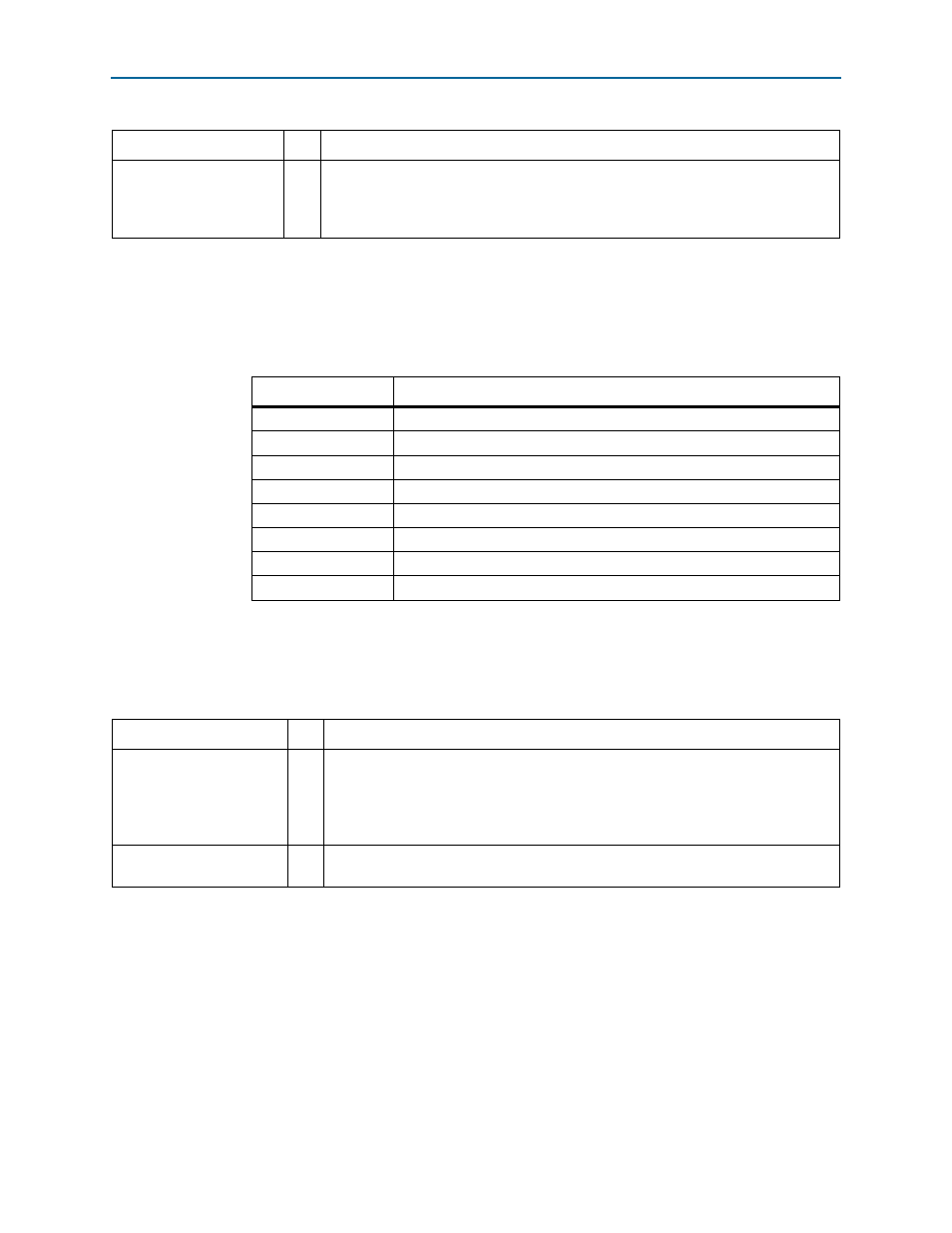

Table B–3. rx_desc[135:128]: Descriptor and BAR Decoding

Bit

Type 0 Component

128

= 1: BAR 0 decoded

129

= 1: BAR 1 decoded

130

= 1: BAR 2 decoded

131

= 1: BAR 3 decoded

132

= 1: BAR 4 decoded

133

= 1: BAR 5 decoded

134

= 1: Expansion ROM decoded

135

Reserved

Note to

(1) Only one bit of [135:128] is asserted at a time.

Table B–4. RX Data Phase Signals (Part 1 of 2)

Signal

I/O

Description

rx_dfr<n>

O

Receive data phase framing. This signal is asserted on the same or subsequent clock

cycle as rx_req to request a data phase (assuming a data phase is needed). It is

deasserted on the clock cycle preceding the last data phase to signal to the application

layer the end of the data phase. The application layer does not need to implement a

data phase counter.

rx_dv<n>

O

Receive data valid. This signal is asserted by the IP core to signify that

rx_data[63:0]

contains data.