Serial interface signals – Altera IP Compiler for PCI Express User Manual

Page 141

Chapter 5: IP Core Interfaces

5–55

Physical Layer Interface Signals

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

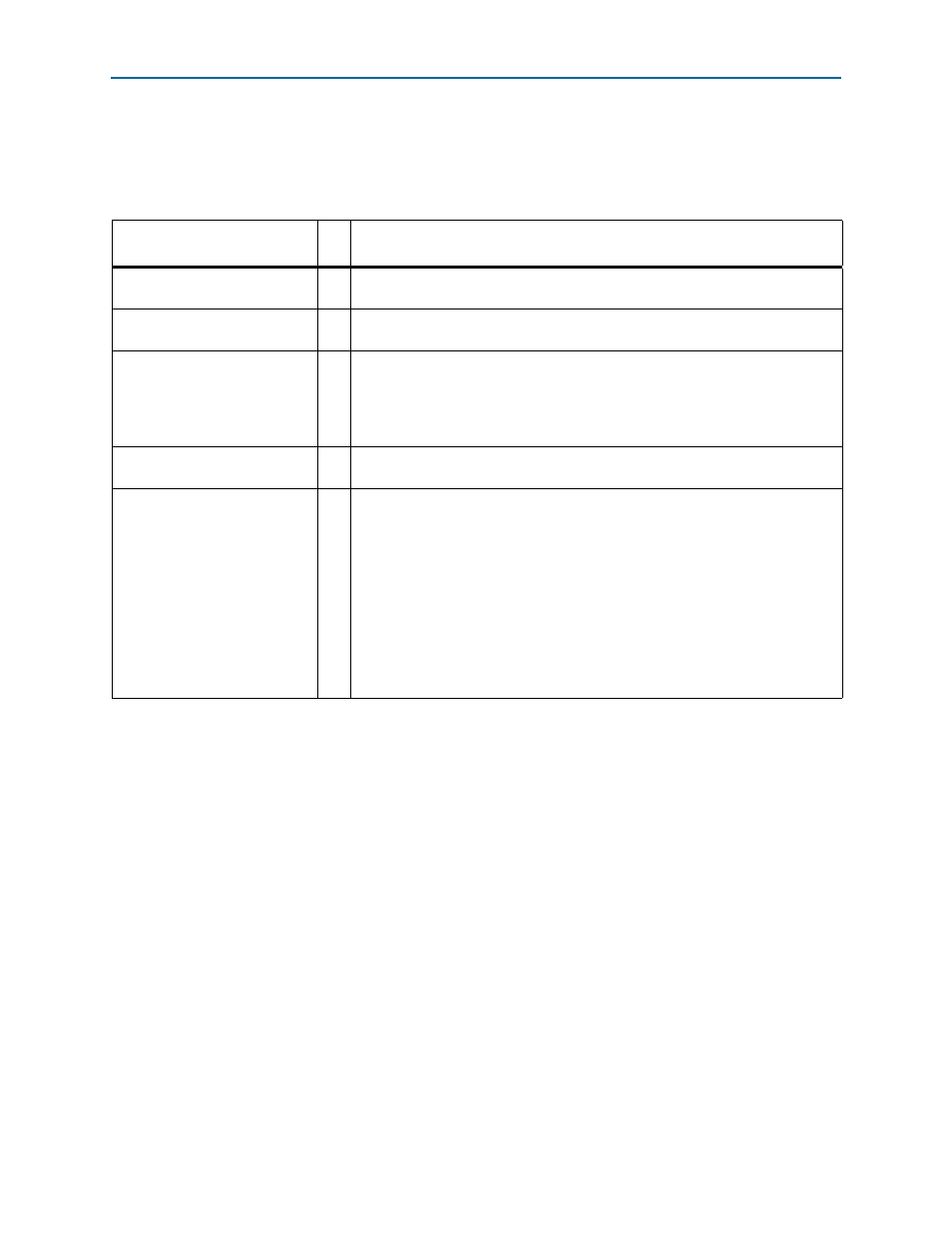

Serial Interface Signals

describes the serial interface signals. These signals are available if you use

the Arria II GX PHY, or Stratix IV GX PHY.

For the soft IP implementation of the ×1 IP core any channel of any transceiver block

can be assigned for the serial input and output signals. For the hard IP

implementation of the ×1 IP core the serial input and output signals must use channel

0 of the master transceiver block associated with that hard IP block.

For the ×4 IP core the serial inputs (rx_in[0-3]) and serial outputs (tx_out[0-3])

must be assigned to the pins associated with the like-number channels of the

transceiver block. The signals rx_in[0]/tx_out[0] must be assigned to the pins

associated with channel 0 of the transceiver block, rx_in[1]/tx_out[1] must be

assigned to the pins associated with channel 1 of the transceiver block, and so on.

Additionally, the ×4 hard IP implementation must use the four channels of the master

transceiver block associated with that hard IP block.

For the ×8 IP core the serial inputs (rx_in[0-3]) and serial outputs (tx_out[0-3])

must be assigned to the pins associated with the like-number channels of the master

transceiver block. The signals rx_in[0]/tx_out[0] must be assigned to the pins

associated with channel 0 of the master transceiver block, rx_in[1]/tx_out[1] must

be assigned to the pins associated with channel 1 of the master transceiver block, and

so on. The serial inputs (rx_in[4-7]) and serial outputs (tx_out[4-7]) must be

Table 5–30. 1-Bit Interface Signals

Signal Name in

Qsys

I/O

Description

tx_out

[0:7]/

tx_out_tx_dataout[0:7]

O

Transmit input. These signals are the serial outputs of lanes 0–7.

rx_in

<0:7>/

rx_in_rx_datain[0:7]

I

Receive input. These signals are the serial inputs of lanes 0–7.

pipe_mode/pipe_mode

I

pipe_mode

selects whether the IP core uses the PIPE interface or the 1-bit

interface. Setting pipe_mode to a 1 selects the PIPE interface, setting it to 0

selects the 1-bit interface. When simulating, you can set this signal to indicate

which interface is used for the simulation. When compiling your design for an

Altera device, set this signal to 0.

xphy_pll_areset

/not available

I

Reset signal to reset the PLL associated with the IP Compiler for PCI Express. This

signal is not supported in Qsys.

xphy_pll_locked/not

available

O

Asserted to indicate that the IP core PLL has locked. May be used to implement an

optional reset controller to guarantee that the external PHY and PLL are stable

before bringing the IP Compiler for PCI Express out of reset. For IP Compiler for

PCI Express variations that require a PLL, the following sequence of events

guarantees the IP core comes out of reset:

a. Deassert xphy_pll_areset to the PLL in the IP Compiler for PCI Express.

b. Wait for xphy_pll_locked to be asserted

c. Deassert reset signal to the IP Compiler for PCI Express.

This signal is not available in Qsys because Qsys does not support the use of an

external PHY.

Note to

:

(1) The ×1 IP core only has lane 0. The ×4 IP core only has lanes 0–3.