Altera IP Compiler for PCI Express User Manual

Page 55

Chapter 3: Parameter Settings

3–19

IP Core Parameters

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

describes the parameters you can set on this page.

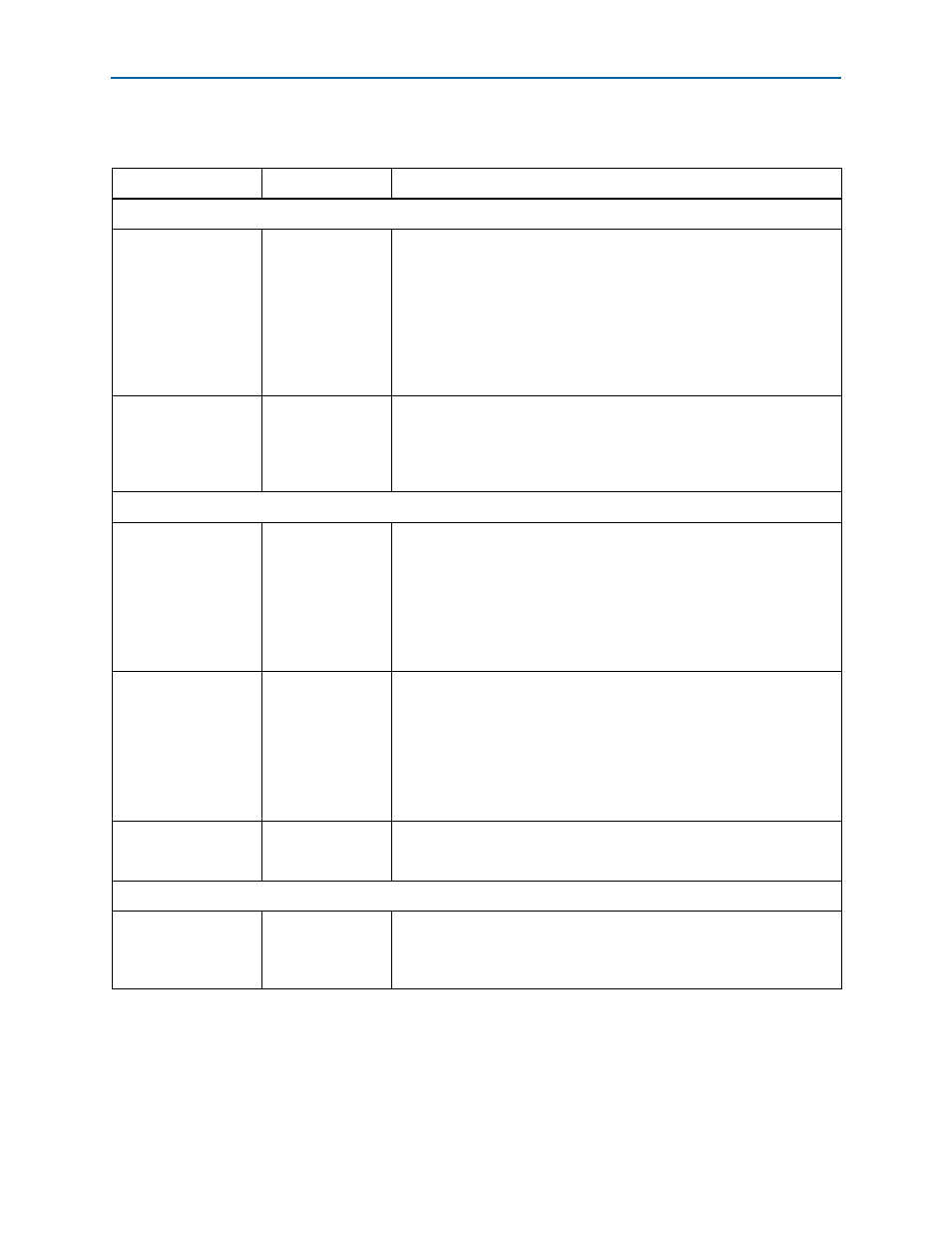

Table 3–13. Power Management Parameters (Part 1 of 2)

Parameter

Value

Description

L0s Active State Power Management (ASPM)

Idle threshold for L0s

entry

256 ns–8,192 ns

(in 256 ns

increments)

This design parameter indicates the idle threshold for L0s entry. This

parameter specifies the amount of time the link must be idle before the

transmitter transitions to L0s state. The PCI Express specification states

that this time should be no more than 7

μs, but the exact value is

implementation-specific. If you select the Arria GX, Arria II GX,

Cyclone IV GX, Stratix II GX, or Stratix IV GX PHY, this parameter is

disabled and set to its maximum value. If you are using an external PHY,

consult the PHY vendor's documentation to determine the correct value for

this parameter.

Endpoint L0s

acceptable latency

< 64 ns – > 4 µs

This design parameter indicates the acceptable endpoint L0s latency for the

device capabilities register. Sets the read-only value of the endpoint L0s

acceptable latency field of the device capabilities register (0x084). This

value should be based on how much latency the application layer can

tolerate. This setting is disabled for root ports.

Number of fast training sequences (N_FTS)

Common clock

Gen1: 0–255

Gen2: 0–255

Indicates the number of fast training sequences needed in common clock

mode. The number of fast training sequences required is transmitted to the

other end of the link during link initialization and is also used to calculate

the L0s exit latency field of the device capabilities register (0x084). If you

select the Arria GX, Arria II GX, Stratix II GX, or Stratix IV GX PHY, this

parameter is disabled and set to its maximum value. If you are using an

external PHY, consult the PHY vendor's documentation to determine the

correct value for this parameter.

Separate clock

Gen1: 0–255

Gen2: 0–255

Indicates the number of fast training sequences needed in separate clock

mode. The number of fast training sequences required is transmitted to the

other end of the link during link initialization and is also used to calculate

the L0s exit latency field of the device capabilities register (0x084). If you

select the Arria GX, Arria II GX, Stratix II GX, or Stratix IV GX PHY, this

parameter is disabled and set to its maximum value. If you are using an

external PHY, consult the PHY vendor's documentation to determine the

correct value for this parameter.

Electrical idle exit

(EIE) before FTS

3:0

Sets the number of EIE symbols sent before sending the N_FTS sequence.

Legal values are 4–8. N_FTS is disabled for Arria II GX and Stratix IV GX

devices pending device characterization.

L1s Active State Power Management (ASPM)

Enable L1 ASPM

On/Off

Sets the L1 active state power management support bit in the link

capabilities register (0x08C). If you select the Arria GX, Arria II GX,

Cyclone IV GX, Stratix II GX, or Stratix IV GX PHY, this option is turned off

and disabled.