Altera IP Compiler for PCI Express User Manual

Page 241

Chapter 15: Testbench and Design Example

15–9

Chaining DMA Design Example

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

■

The design example exercises the optional ECRC module when targeting the hard

IP implementation using a variation with both Implement advanced error

reporting

and ECRC forwarding set to On in the

■

The design example exercises the optional IP Compiler for PCI Express

reconfiguration block when targeting the hard IP implementation if you selected

PCIe Reconfig

on the System Settings page.

environment.

The example endpoint design application layer accomplishes the following objectives:

■

Shows you how to interface to the IP Compiler for PCI Express in Avalon-ST

mode, or in descriptor/data mode through the ICM. Refer to

Compiler for PCI Express Core with the Descriptor/Data Interface

■

Provides a chaining DMA channel that initiates memory read and write

transactions on the PCI Express link.

■

If the ECRC forwarding functionality is enabled, provides a CRC Compiler IP core

to check the ECRC dword from the Avalon-ST RX path and to generate the ECRC

for the Avalon-ST TX path.

■

If the IP Compiler for PCI Express reconfiguration block functionality is enabled,

provides a test that increments the Vendor ID register to demonstrate this

functionality.

You can use the example endpoint design in the testbench simulation and compile a

complete design for an Altera device. All of the modules necessary to implement the

design example with the variation file are contained in one of the following files,

based on the language you use:

<variation name>_examples/chaining_dma/example_chaining.vhd

or

<variation name>_examples/chaining_dma/example_chaining.v

These files are created in the project directory when files are generated.

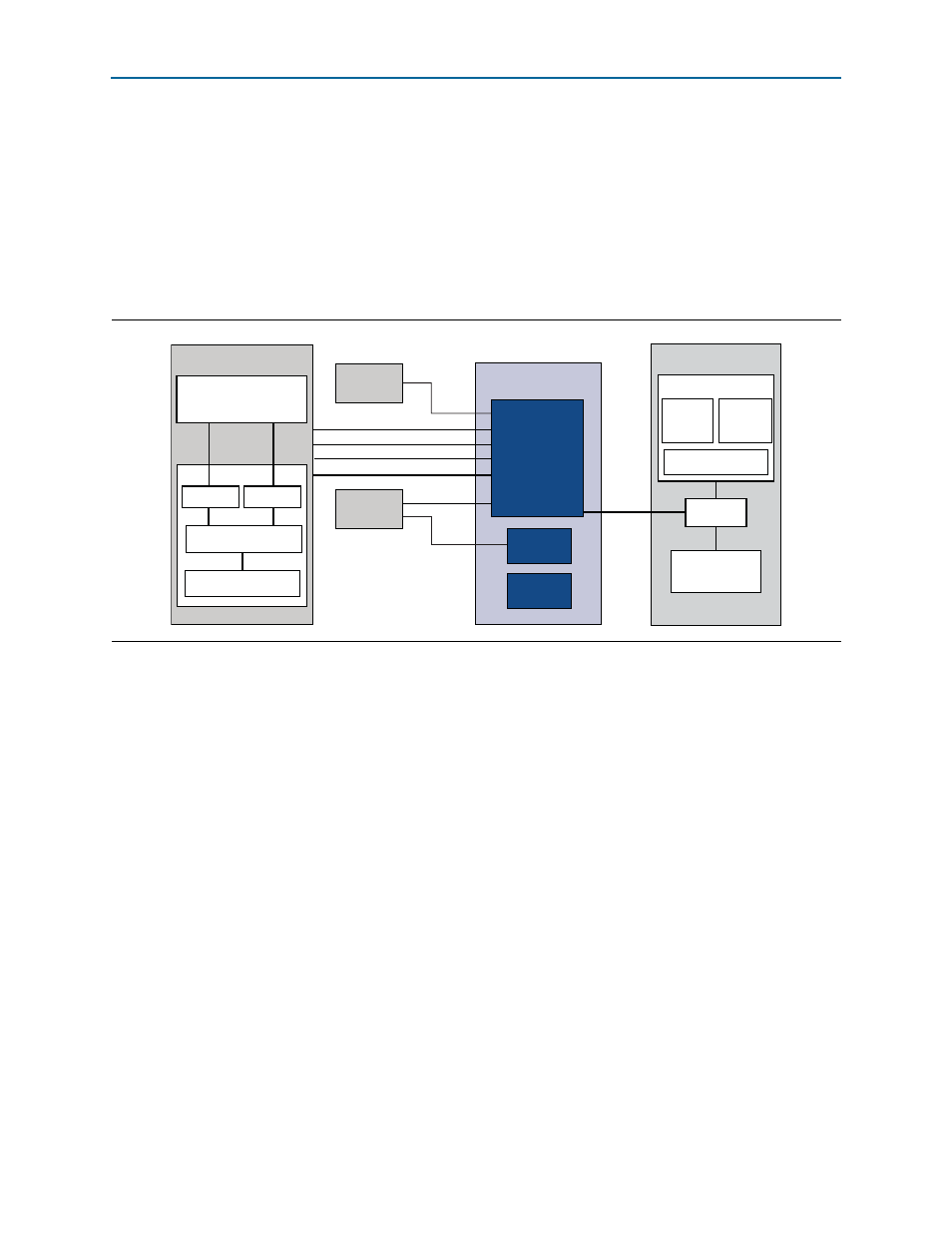

Figure 15–4. Top-Level Chaining DMA Example for Simulation—Hard IP Implementation with PCIE Reconfig Block

Root Complex

<variant>_plus

CPU

Root Port

Memory

Read

Descriptor

Table

Write

Descriptor

Table

Data

Chaining DMA

Endpoint Memory

Avalon-MM

interfaces

IP Compiler

for PCI Express

(Hard IP

Implementation)

Reset

Calibration

Control Register

DMA Read

Avalon-ST

Avalon-MM

Configuration

PCI Express

DMA Write

RC Slave

PCIE Reconfig

Driver

CBB Test

Driver

to test_in[5,32] altpcierd_compliance_test.v