Mapping of avalon-st packets to pci express tlps, Refer to, Figure 5–16 – Altera IP Compiler for PCI Express User Manual

Page 104

5–18

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

illustrates the TLP fields of the tx_cred bus. For completion header,

non-posted header, non-posted data and posted header fields, a saturation value of

seven indicates seven or more available transmit credits.

For the hard IP implementation in Arria II GX, Arria II GZ, and Stratix IV GX devices,

a saturation value of six or greater should be used for non-posted header and

non-posted data. If your system allocates a single non-posted credit, you can use the

receipt of completions to detect the release of credit for non-posted writes.

Mapping of Avalon-ST Packets to PCI Express TLPs

through

illustrate the mappings between Avalon-ST packets

and PCI Express TLPs. These mappings apply to all types of TLPs, including posted,

non-posted and completion. Message TLPs use the mappings shown for four dword

headers. TLP data is always address-aligned on the Avalon-ST interface whether or

not the lower dwords of the header contain a valid address as may be the case with

TLP type (message request with data payload).

f

For additional information about TLP packet headers, refer to

Transaction Layer Packet (TLP) Header Formats

and Section 2.2.1 Common Packet

Header Fields in the

illustrates the mapping between Avalon-ST TX packets and PCI Express

TLPs for 3 dword header TLPs with non-qword aligned addresses with a 64-bit bus.

(

illustrates the storage of non-qword aligned data.)

Figure 5–16. TX Credit Signal

35

24

23

21 20

18

17

15

14

3 2

0

Completion Data

Comp Hdr

NPData

NP Hdr

Posted Data

Posted

Header

Note to

(1) When infinite credits are available, the corresponding credit field is all 1's.

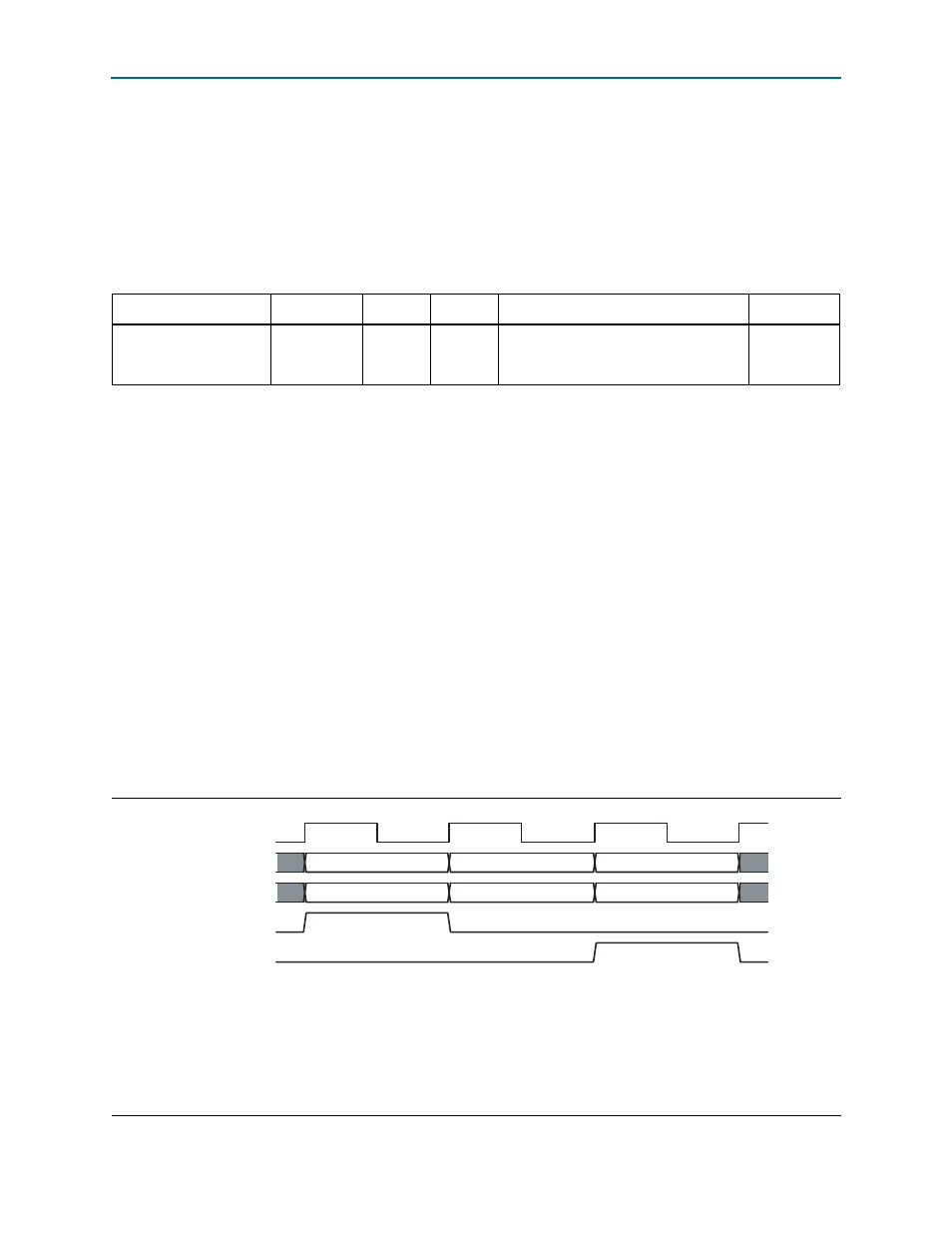

Figure 5–17. 64-Bit Avalon-ST tx_st_data Cycle Definition for 3-DWord Header TLP with Non-QWord Aligned Address

Notes to

:

(1) Header0 ={pcie_hdr_byte0, pcie_hdr _byte1, pcie_hdr _byte2, pcie_hdr _byte3}

(2) Header1 = {pcie_hdr_byte4, pcie_hdr _byte5, header pcie_hdr byte6, pcie_hdr _byte7}

(3) Header2 = {pcie_hdr _byte8, pcie_hdr _byte9, pcie_hdr _byte10, pcie_hdr _byte11}

(4) Data0 = {pcie_data_byte3, pcie_data_byte2, pcie_data_byte1, pcie_data_byte0}

(5) Data1 = {pcie_data_byte7, pcie_data_byte6, pcie_data_byte5, pcie_data_byte4}

(6) Data2 = {pcie_data_byte11, pcie_data_byte10, pcie_data_byte9, pcie_data_byte8}.

clk

tx_st_data[63:32]

tx_st_data[31:0]

tx_st_sop

tx_st_eop

Header1

Data0

Data2

Header0

Header2

Data1

1

2

3