Avalon-mm-to-pci express read completions, Pci express-to-avalon-mm address translation – Altera IP Compiler for PCI Express User Manual

Page 79

Chapter 4: IP Core Architecture

4–21

PCI Express Avalon-MM Bridge

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

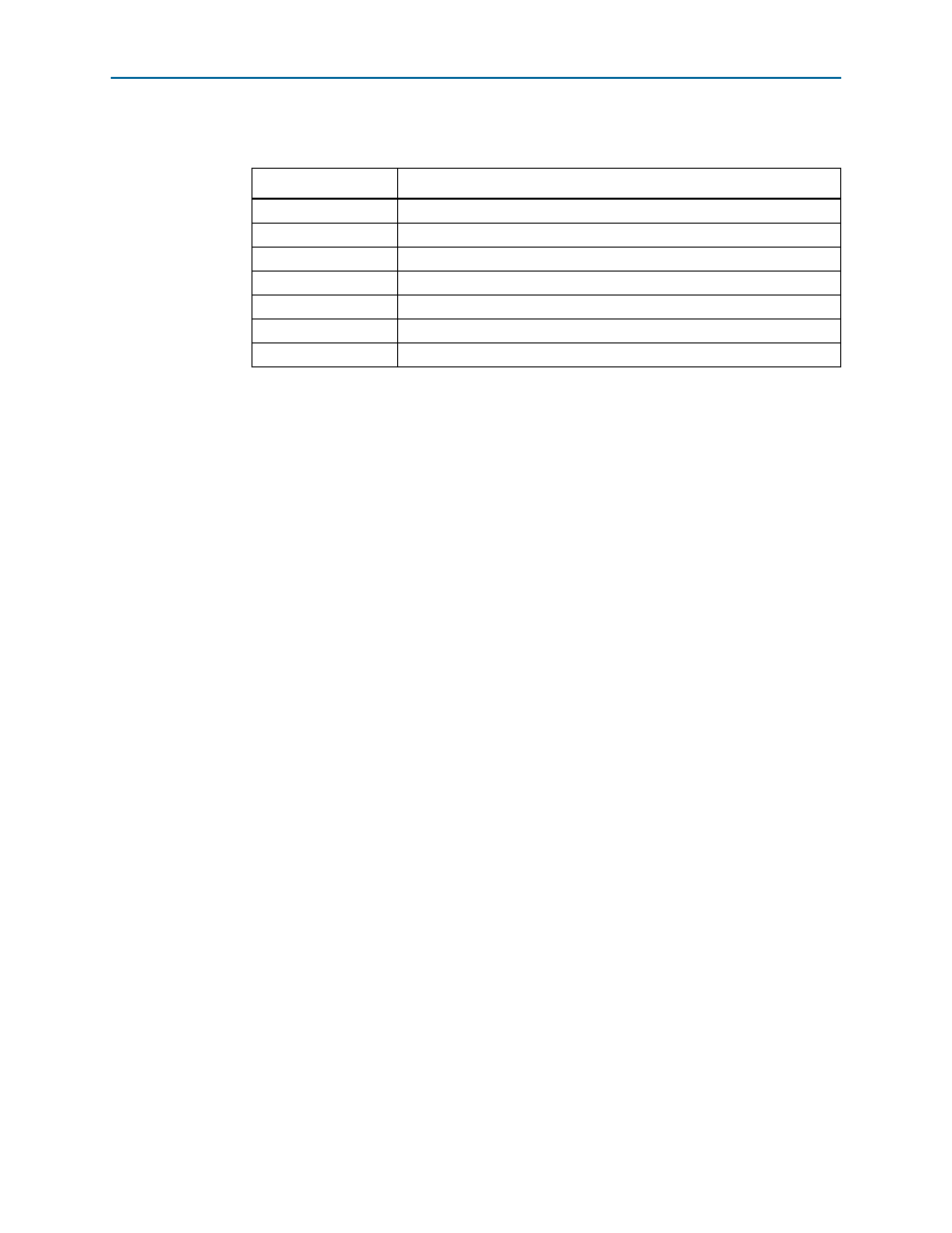

As an example,

lists the byte enables for 32-bit data.

In burst mode, the IP Compiler for PCI Express supports only byte enable values that

correspond to a contiguous data burst. For the 32-bit data width example, valid values

in the first data phase are 4’b1111, 4’b1100, and 4’b1000, and valid values in the final

data phase of the burst are 4’b1111, 4’b0011, and 4’b0001. Intermediate data phases in

the burst can only have byte enable value 4’b1111.

Avalon-MM-to-PCI Express Read Completions

The PCI Express Avalon-MM bridge converts read response data from the external

Avalon-MM slave to PCI Express completion packets and sends them to the

transaction layer.

A single read request may produce multiple completion packets based on the

Maximum Payload Size

and the size of the received read request. For example, if the

read is 512 bytes but the Maximum Payload Size 128 bytes, the bridge produces four

completion packets of 128 bytes each. The bridge does not generate out-of-order

completions. You can specify the Maximum Payload Size parameter on the Buffer

Setup page of the IP Compiler for PCI Express parameter editor. Refer to

Setup Parameters” on page 3–16

.

PCI Express-to-Avalon-MM Address Translation

The PCI Express address of a received request packet is translated to the Avalon-MM

address before the request is sent to the system interconnect fabric. This address

translation proceeds by replacing the MSB bits of the PCI Express address with the

value from a specific translation table entry; the LSB bits remain unchanged. The

number of MSB bits to replace is calculated from the total memory allocation of all

Avalon-MM slaves connected to the RX Master Module port. Six possible address

translation entries in the address translation table are configurable manually by Qsys.

Each entry corresponds to a PCI Express BAR. The BAR hit information from the

request header determines the entry that is used for address translation.

Table 4–2. Valid Byte Enable Configurations

Byte Enable Value

Description

4’b1111

Write full 32 bits

4’b0011

Write the lower 2 bytes

4’b1100

Write the upper 2 bytes

4’b0001

Write byte 0 only

4’b0010

Write byte 1 only

4’b0100

Write byte 2 only

4’b1000

Write byte 3 only