Device identification registers – Altera IP Compiler for PCI Express User Manual

Page 39

Chapter 3: Parameter Settings

3–3

Parameters in the Qsys Design Flow

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

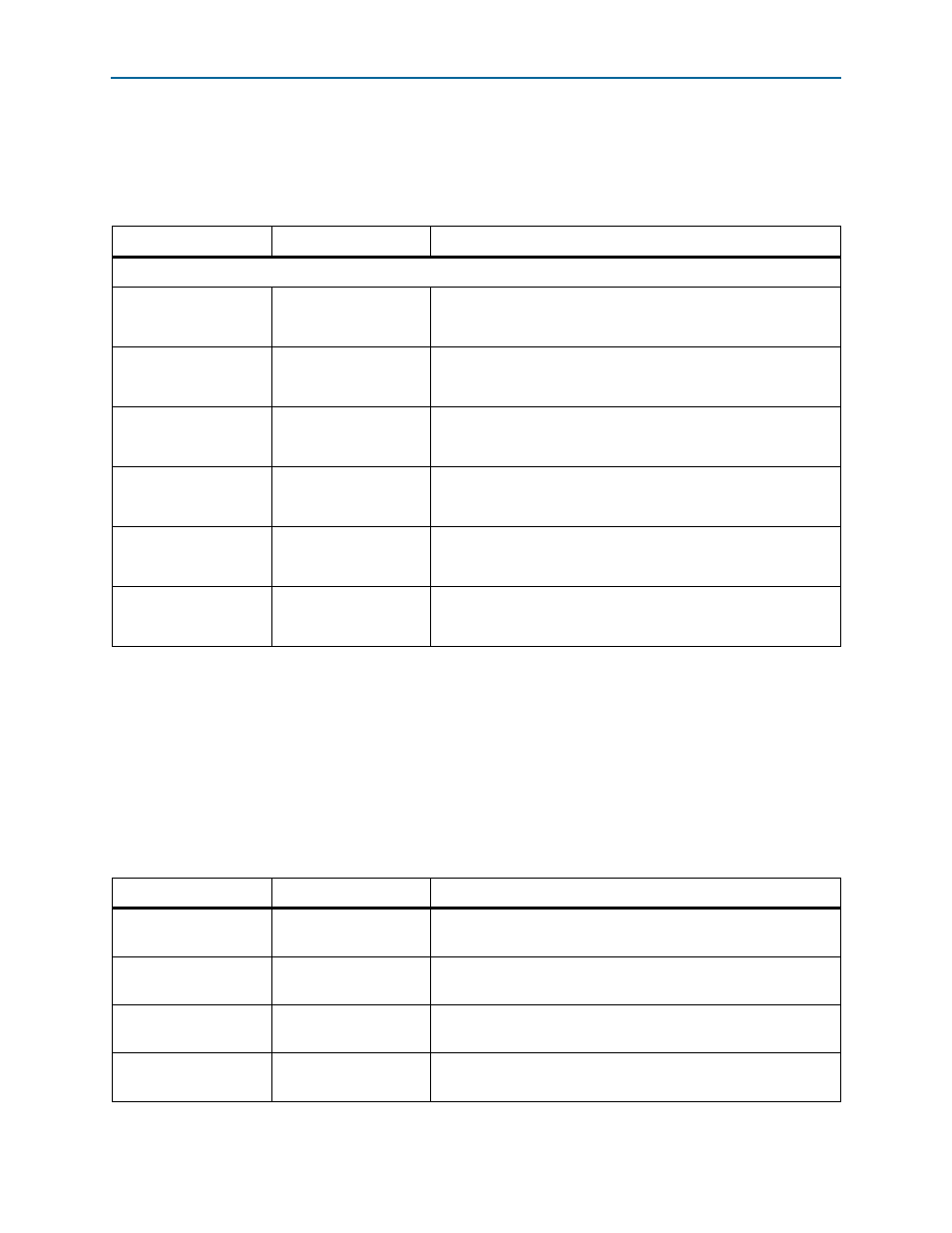

describes the PCI register parameters. You can configure a BAR with value

other than Not used only if the preceding BARs are configured. When an

even-numbered BAR is set to 64 bit Prefetchable, the following BAR is labelled

Occupied

and forced to value Not used.

Device Identification Registers

The device identification registers are part of the PCI Type 0 configuration space

header. You can set these register values only at device configuration.

describes the PCI read-only device identification registers.

Table 3–2. PCI Registers

Parameter

Value

Description

PCI Base Address Registers (0x10, 0x14, 0x18, 0x1C, 0x20, 0x24)

BAR Table (BAR0)

BAR Type

64 bit Prefetchable

32 but Non-Prefetchable

Not used

BAR0 size and type mapping (memory space). BAR0 and BAR1 can

be combined to form a 64-bit prefetchable BAR. BAR0 and BAR1 can

be configured separately as 32-bit non-prefetchable memories.)

BAR Table (BAR1)

BAR Type

32 but Non-Prefetchable

Not used

BAR1 size and type mapping (memory space). BAR0 and BAR1 can

be combined to form a 64-bit prefetchable BAR. BAR0 and BAR1 can

be configured separately as 32-bit non-prefetchable memories.)

BAR Table (BAR2)

BAR Type

64 bit Prefetchable

32 but Non-Prefetchable

Not used

BAR2 size and type mapping (memory space). BAR2 and BAR3 can

be combined to form a 64-bit prefetchable BAR. BAR2 and BAR3 can

be configured separately as 32-bit non-prefetchable memories.)

BAR Table (BAR3)

BAR Type

32 but Non-Prefetchable

Not used

BAR3 size and type mapping (memory space). BAR2 and BAR3 can

be combined to form a 64-bit prefetchable BAR. BAR2 and BAR3 can

be configured separately as 32-bit non-prefetchable memories.)

BAR Table (BAR4)

BAR Type

64 bit Prefetchable

32 but Non-Prefetchable

Not used

BAR4 size and type mapping (memory space). BAR4 and BAR5 can

be combined to form a 64-bit BAR. BAR4 and BAR5 can be

configured separately as 32-bit non-prefetchable memories.)

BAR Table (BAR5)

BAR Type

32 but Non-Prefetchable

Not used

BAR5 size and type mapping (memory space). BAR4 and BAR5 can

be combined to form a 64-bit BAR. BAR4 and BAR5 can be

configured separately as 32-bit non-prefetchable memories.)

Notes to

(1) A prefetchable 64-bit BAR is supported. A non-prefetchable 64-bit BAR is not supported because in a typical system, the root port configuration

register of type 1 sets the maximum non-prefetchable memory window to 32-bits.

(2) The Qsys design flow does not support I/O space for BAR type mapping. I/O space is only supported for legacy endpoint port types.

Table 3–3. PCI Registers (Part 1 of 2)

Parameter

Value

Description

Vendor ID

0x1172

Sets the read-only value of the vendor ID register. This parameter

can not be set to 0xFFFF per the PCI Express Specification.

Device ID

0x0004

Sets the read-only value of the device ID register.

Revision ID

0x01

Sets the read-only value of the revision ID register.

Class code

0xFF0000

Sets the read-only value of the class code register.