Altera IP Compiler for PCI Express User Manual

Page 228

14–8

Chapter 14: External PHYs

External PHY Support

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

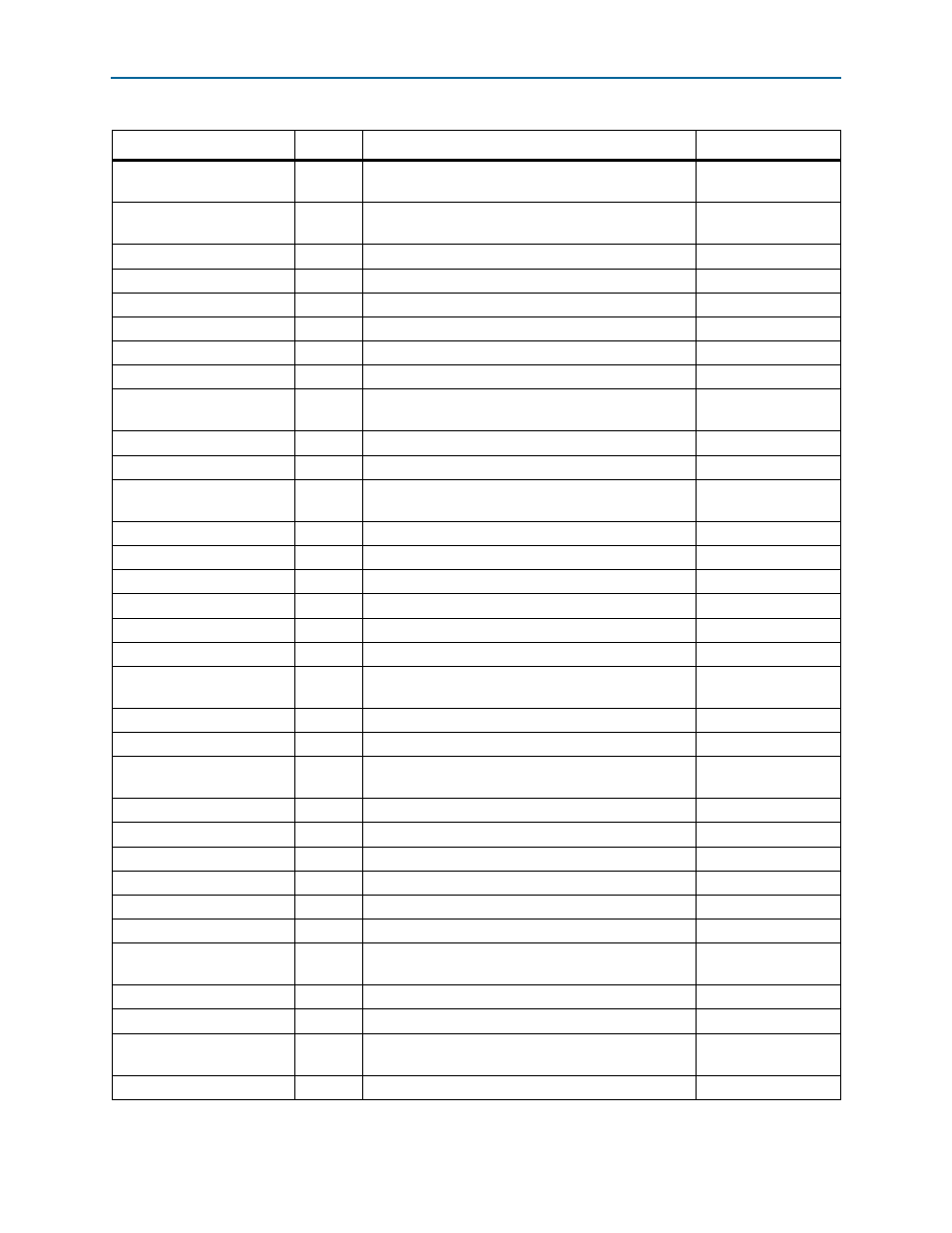

pipe_txclk

O

Source synchronous transmit clock signal for clocking

TX Data and Control signals going to the PHY.

Only in modes that

have the TXClk

rxdata0_ext[15:0]

I

Pipe interface lane 0 RX data signals, carries the

parallel received data.

Always

rxdatak0_ext[1:0]

I

Pipe interface lane 0 RX data K-character flags.

Always

rxelecidle0_ext

I

Pipe interface lane 0 RX electrical idle indication.

Always

rxpolarity0_ext

O

Pipe interface lane 0 RX polarity inversion control.

Always

rxstatus0_ext[1:0]

I

Pipe interface lane 0 RX status flags.

Always

rxvalid0_ext

I

Pipe interface lane 0 RX valid indication.

Always

txcompl0_ext

O

Pipe interface lane 0 TX compliance control.

Always

txdata0_ext[15:0]

O

Pipe interface lane 0 TX data signals, carries the

parallel transmit data.

Always

txdatak0_ext[1:0]

O

Pipe interface lane 0 TX data K-character flags.

Always

txelecidle0_ext

O

Pipe interface lane 0 TX electrical Idle Control.

Always

rxdata1_ext[15:0]

I

Pipe interface lane 1 RX data signals, carries the

parallel received data.

Only in ×4

rxdatak1_ext[1:0]

I

Pipe interface lane 1 RX data K-character flags.

Only in ×4

rxelecidle1_ext

I

Pipe interface lane 1 RX electrical idle indication.

Only in ×4

rxpolarity1_ext

O

Pipe interface lane 1 RX polarity inversion control.

Only in ×4

rxstatus1_ext[1:0]

I

Pipe interface lane 1 RX status flags.

Only in ×4

rxvalid1_ext

I

Pipe interface lane 1 RX valid indication.

Only in ×4

txcompl1_ext

O

Pipe interface lane 1 TX compliance control.

Only in ×4

txdata1_ext[15:0]

O

Pipe interface lane 1 TX data signals, carries the

parallel transmit data.

Only in ×4

txdatak1_ext[1:0]

O

Pipe interface lane 1 TX data K-character flags.

Only in ×4

txelecidle1_ext

O

Pipe interface lane 1 TX electrical idle control.

Only in ×4

rxdata2_ext[15:0]

I

Pipe interface lane 2 RX data signals, carries the

parallel received data.

Only in ×4

rxdatak2_ext[1:0]

I

Pipe interface lane 2 RX data K-character flags.

Only in ×4

rxelecidle2_ext

I

Pipe interface lane 2 RX electrical idle indication.

Only in ×4

rxpolarity2_ext

O

Pipe interface lane 2 RX polarity inversion control.

Only in ×4

rxstatus2_ext[1:0]

I

Pipe interface lane 2 RX status flags.

Only in ×4

rxvalid2_ext

I

Pipe interface lane 2 RX valid indication.

Only in ×4

txcompl2_ext

O

Pipe interface lane 2 TX compliance control.

Only in ×4

txdata2_ext[15:0]

O

Pipe interface lane 2 TX data signals, carries the

parallel transmit data.

Only in ×4

txdatak2_ext[1:0]

O

Pipe interface lane 2 TX data K-character flags.

Only in ×4

txelecidle2_ext

O

Pipe interface lane 2 TX electrical idle control.

Only in ×4

rxdata3_ext[15:0]

I

Pipe interface lane 3 RX data signals, carries the

parallel received data.

Only in ×4

rxdatak3_ext[1:0]

I

Pipe interface lane 3 RX data K-character flags.

Only in ×4

Table 14–2. 16-bit PHY Interface Signals (Part 2 of 3)

Signal Name

Direction

Description

Availability