Altera IP Compiler for PCI Express User Manual

Page 212

13–2

Chapter 13: Reconfiguration and Offset Cancellation

Dynamic Reconfiguration

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

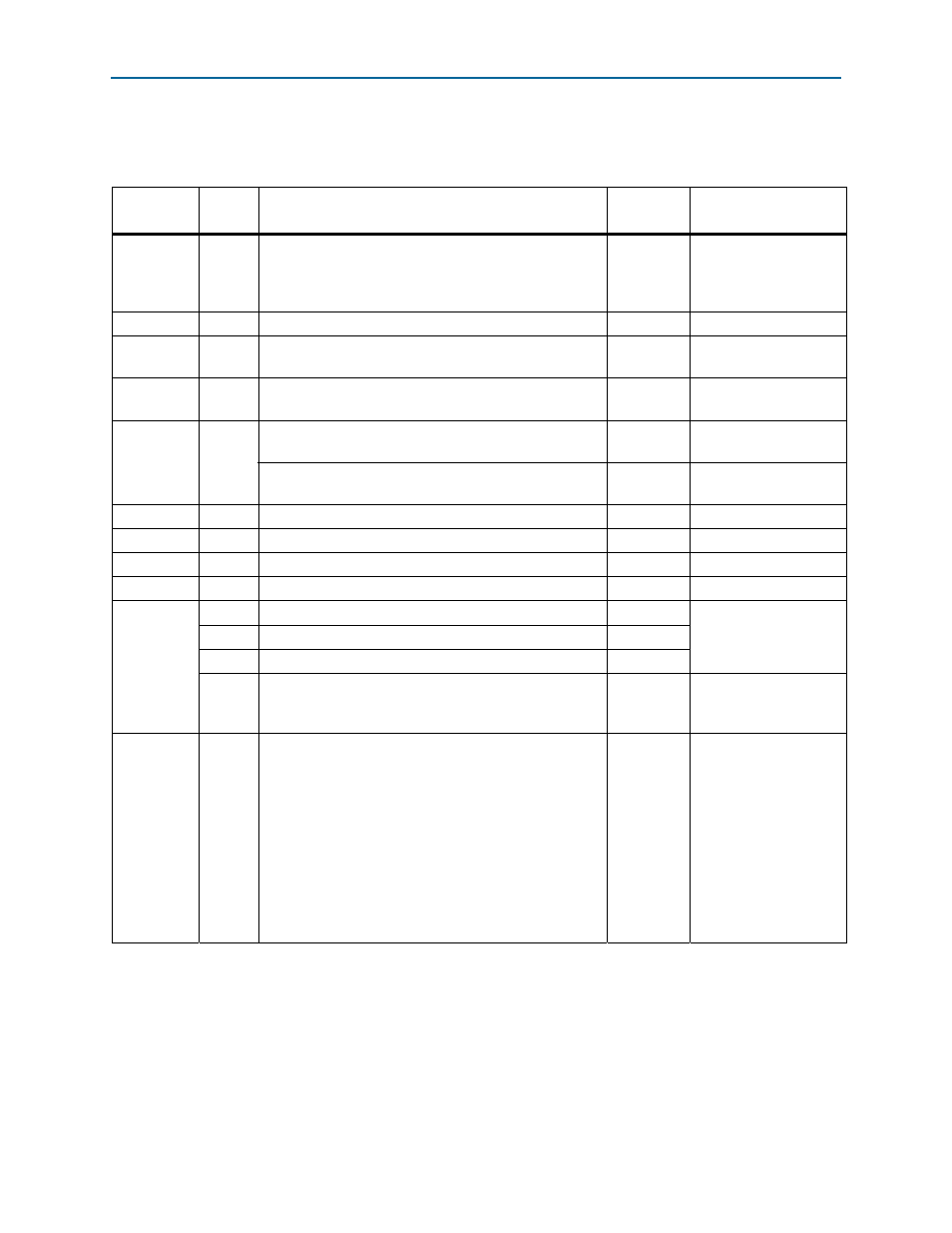

lists all of the registers that you can update using the IP Compiler for PCI

Express reconfiguration block interface.

Table 13–1. Dynamically Reconfigurable Registers in the Hard IP Implementation (Part 1 of 7)

Address

Bits

Description

Default

Value

Additional Information

0x00

0

When 0, PCIe reconfig mode is enabled. When 1, PCIe

reconfig mode is disabled and the original read only

register values set in the programming file used to

configure the device are restored.

b’1

—

0x01-0x88

Reserved.

—

0x89

15:0 Vendor ID.

0x1172

0x8A

15:0 Device ID.

0x0001

0x8B

7:0

15:8

Revision ID.

0x01

Class code[7:0].

—

0x8C

15:0 Class code[23:8].

—

0x8D

15:0 Subsystem vendor ID.

0x1172

0x8E

15:0 Subsystem device ID.

0x0001

0x8F

Reserved.

—

0x90

0 Advanced Error Reporting.

b’0

Port VC Cap 1

3:1 Low Priority VC (LPVC).

b’000

7:4 VC arbitration capabilities.

b’00001

15:8 Reject Snoop Transaction.d

b’00000000

VC Resource Capability

register

2:0

Max payload size supported. The following are the defined

encodings:

b’010

Device Capability

register

000: 128 bytes max payload size.

001: 256 bytes max payload size.

010: 512 bytes max payload size.

011: 1024 bytes max payload size.

100: 2048 bytes max payload size.

101: 4096 bytes max payload size.

110: Reserved.

111: Reserved.