Altera IP Compiler for PCI Express User Manual

Page 131

Chapter 5: IP Core Interfaces

5–45

Avalon-MM Application Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

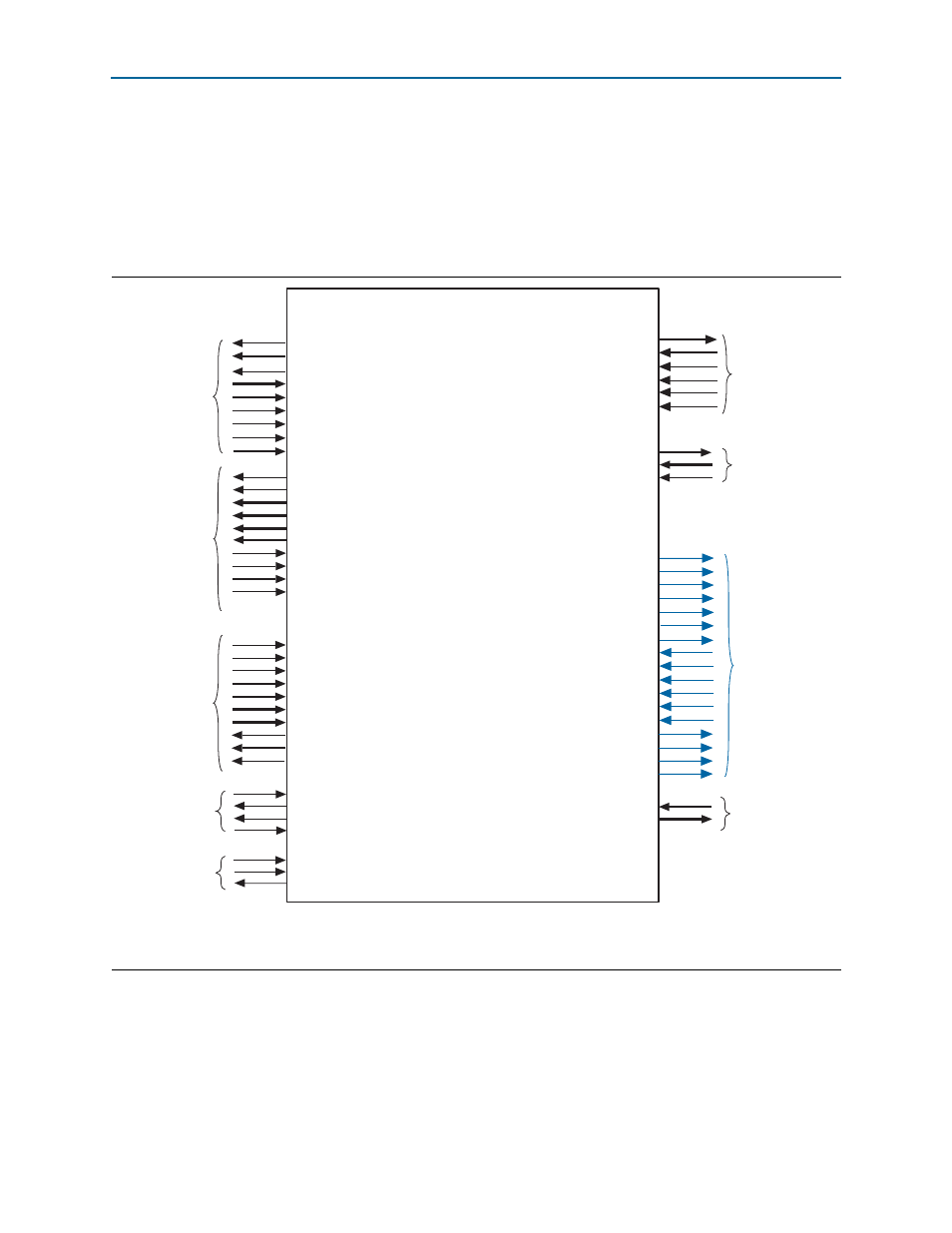

shows all the signals of a full-featured IP Compiler for PCI Express

available in the Qsys design flow. Your parameterization may not include some of the

ports. The Avalon-MM signals are shown on the left side of this figure.

1

The IP Compiler for PCI Express available in the Qsys design flow does not support

the use of an external PHY.

Figure 5–37. Signals in the Qsys Hard Full-Featured IP Core with Avalon-MM Interface

Note to

(1) Signals in blue are for simulation only.

tx_out_tx_dataout[3:0]

rx_in_rx_datain[3:0]

pipe_mode

1-Bit Serial

CraIrq_irq

Cra_readdata[31:0]

Cra_waitrequest

Cra_byteenable[3:0]

Cra_chipselect

Cra_address[11:0]

Cra_read

Cra_write

Cra_writedata[31:0]

Txs_writedata[63:0]

Txs_read

Txs_chipselect

Txs_waitrequest

Txs_write

Txs_byteenable[7:0]

Txs_burstcount[6:0]

Txs_readdatavalid

Txs_readdata[63:0]

Txs_address[19:0]

32-Bit

Avalon-MM

CRA

Slave Port

64-Bit

Avalon-MM Tx

Slave Port

avalon_reset_reset

Clock

Reset &

Status

pcie_core_clk_clk

pcie_core_reset_reset_n

avalon_clk_clk

refclk_export

pcie_rstn_export

suc_spd_neg

Signals in the IP Compiler for PCI Express

with Avalon-MM Interface (Qsys)

Test

Interface

test_out_test_out[63:0]

test_in_test_in[39:0]

(test_out is optional)

reconfig_fromgxb_data[

<n>

:0]

reconfig_togxb_data[

<n>

:0]

reconfig_gxbclk_clk

cal_blk_clk_clk

pipe_ext_gxb_powerdown

fixedclk_serdes

Transceiver

Control

Bar

<a>_<b>_

read

<n>

Bar

<a>_<b>_

write

<n>

Bar

<a>_<b>_

address

<n>

[

<w>

-1:0]

Bar

<a>_<b>_

writedata

<n>

[63:0]

Bar

<a>_<b>_

byteenable

<n>

[7:0]

Bar

<a>_<b>_

burstcount

<n>

[6:0]

Bar

<a>_<b>_

waitrequest

<n>

Bar

<a>_<b>_

readdatavalid

<n>

Bar

<a>_<b>_

readdata

<n>

[63:0]

RxmIrq[N:0], N < 16

64-Bit

Avalon-MM Rx

Master Port

txdatak0_ext

txdata0_ext[7:0]

txdetectrx_ext

txelectidle0_ext

rxpolarity0_ext

txcompl0_ext

powerdown0_ext[1:0]

rxdata0_ext[7:0]

rxdatak0_ext

rxvalid0_ext

phystatus_ext

rxelectidle0_ext

rxstatus0_ext[2:0]

rate_ext

clocks_sim_clk125_export

clocks_sim_clk500_export

clocks_sim_clk250_export

Hard IP

Implementation

Simulation

Only

8-Bit PIPE

(1)