Altera IP Compiler for PCI Express User Manual

Page 214

13–4

Chapter 13: Reconfiguration and Offset Cancellation

Dynamic Reconfiguration

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

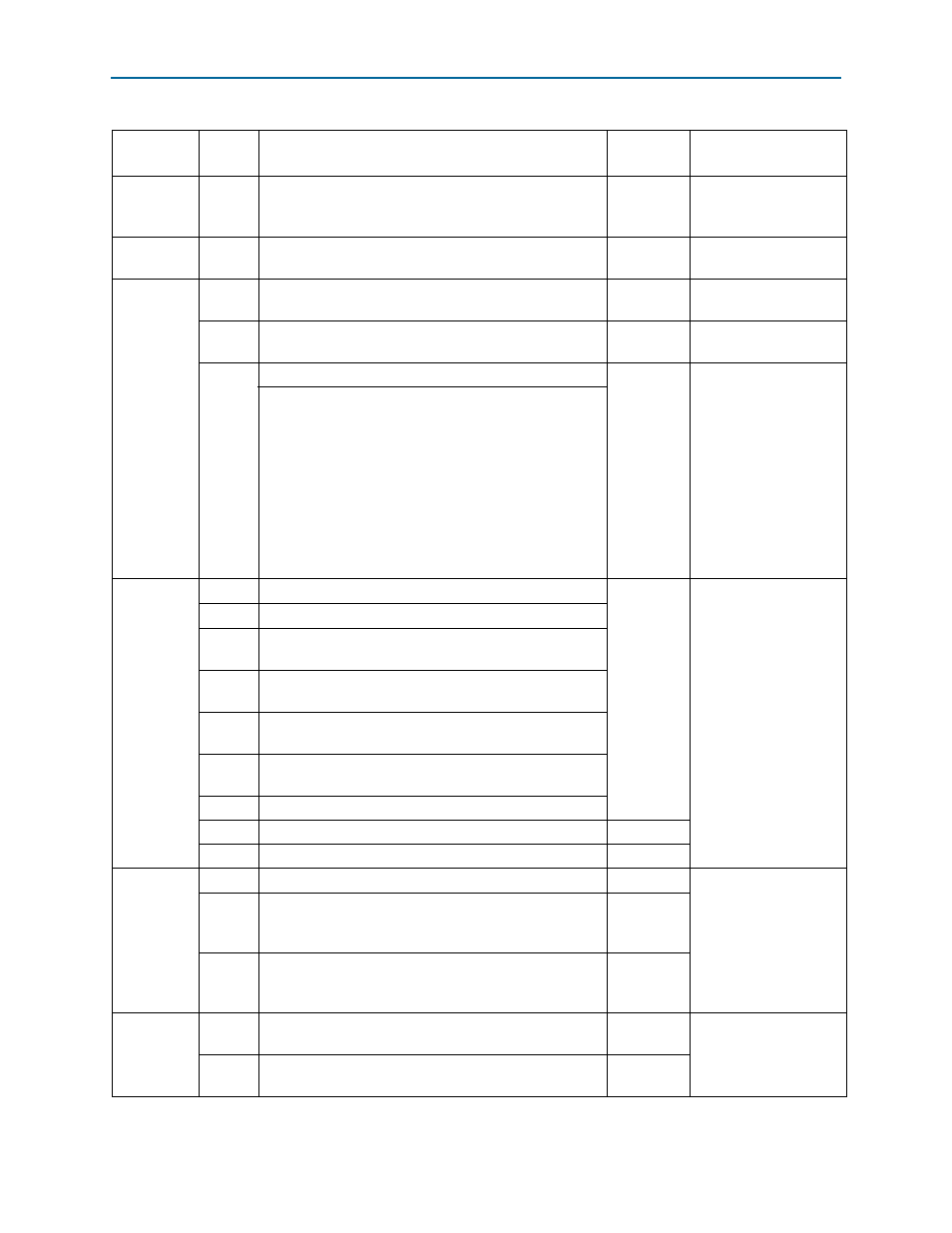

0x91

15

Role-Based error reporting. (Available in PCI Express Base

Specification Revision 1.1 compliant Cores only.)In 1.1

compliant cores, this bit should be set to 1.

b’1

,

Correctable Error Mask

register

1:0 Slot Power Limit Scale.

b’00

Slot Capability register

0x92

7:2 Max Link width.

b’000100

Link Capability register

9:8

L0s Active State power management support.

L1 Active State power management support.

b’01

Link Capability register

15:10

L1 exit latency common clock.

b’000000

Link Capability register

L1 exit latency separated clock. The following encodings

are defined:

b’000 – Less than 1 µs.

b’001 – 1 µs to less than 2 µs.

b’010 – 2 µs to less than 4 µs.

b’011 – 4 µs to less than 8 µs.

b’100 – 8 µs to less than 16 µs.

b’101 – 16 µs to less than 32 µs.

b’110 – 32 µs to 64 µs.

b’111 – More than 64 µs.

0x93

[0]: Attention button implemented on the chassis.

b’0000000

Slot Capability register

[1]: Power controller present.

[2]: Manually Operated Retention Latch (MRL) sensor

present.

[3]: Attention indicator present for a root port, switch, or

bridge.

[4]: Power indicator present for a root port, switch, or

bridge.

[5]: Hot-plug surprise: When this bit set to1, a device can

be removed from this slot without prior notification.

6:0 [6]: Hot-plug capable.

9:7 Reserved.

b’000

15:10 Slot Power Limit Value.

b’00000000

0x94

1:0 Reserved.

—

Slot Capability register

2

Electromechanical Interlock present (Available in PCI

Express Base Specification Revision 1.1 compliant IP

cores only.)

b’0

15:3

Physical Slot Number (if slot implemented). This signal

indicates the physical slot number associated with this

port. It must be unique within the fabric.

b’0

0x95

7:0

NFTS_SEPCLK. The number of fast training sequences for

the separate clock.

b’10000000

—

15:8

NFTS_COMCLK. The number of fast training sequences

for the common clock.

b’10000000

Table 13–1. Dynamically Reconfigurable Registers in the Hard IP Implementation (Part 3 of 7)

Address

Bits

Description

Default

Value

Additional Information