Simulation environment, Compatibility testing environment, Performance and resource utilization – Altera IP Compiler for PCI Express User Manual

Page 12

1–10

Chapter 1: Datasheet

Performance and Resource Utilization

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Simulation Environment

Altera’s verification simulation environment for the IP Compiler for PCI Express uses

multiple testbenches that consist of industry-standard BFMs driving the PCI Express

link interface. A custom BFM connects to the application-side interface.

Altera performs the following tests in the simulation environment:

■

Directed tests that test all types and sizes of transaction layer packets and all bits of

the configuration space

■

Error injection tests that inject errors in the link, transaction layer packets, and data

link layer packets, and check for the proper response from the IP cores

■

PCI-SIG

®

Compliance Checklist tests that specifically test the items in the checklist

■

Random tests that test a wide range of traffic patterns across one or more virtual

channels

Compatibility Testing Environment

Altera has performed significant hardware testing of the IP Compiler for PCI Express

to ensure a reliable solution. The IP cores have been tested at various PCI-SIG PCI

Express Compliance Workshops in 2005–2009 with Arria GX, Arria II GX,

Cyclone IV GX, Stratix II GX, and Stratix IV GX devices and various external PHYs.

They have passed all PCI-SIG gold tests and interoperability tests with a wide

selection of motherboards and test equipment. In addition, Altera internally tests

every release with motherboards and switch chips from a variety of manufacturers.

All PCI-SIG compliance tests are also run with each IP core release.

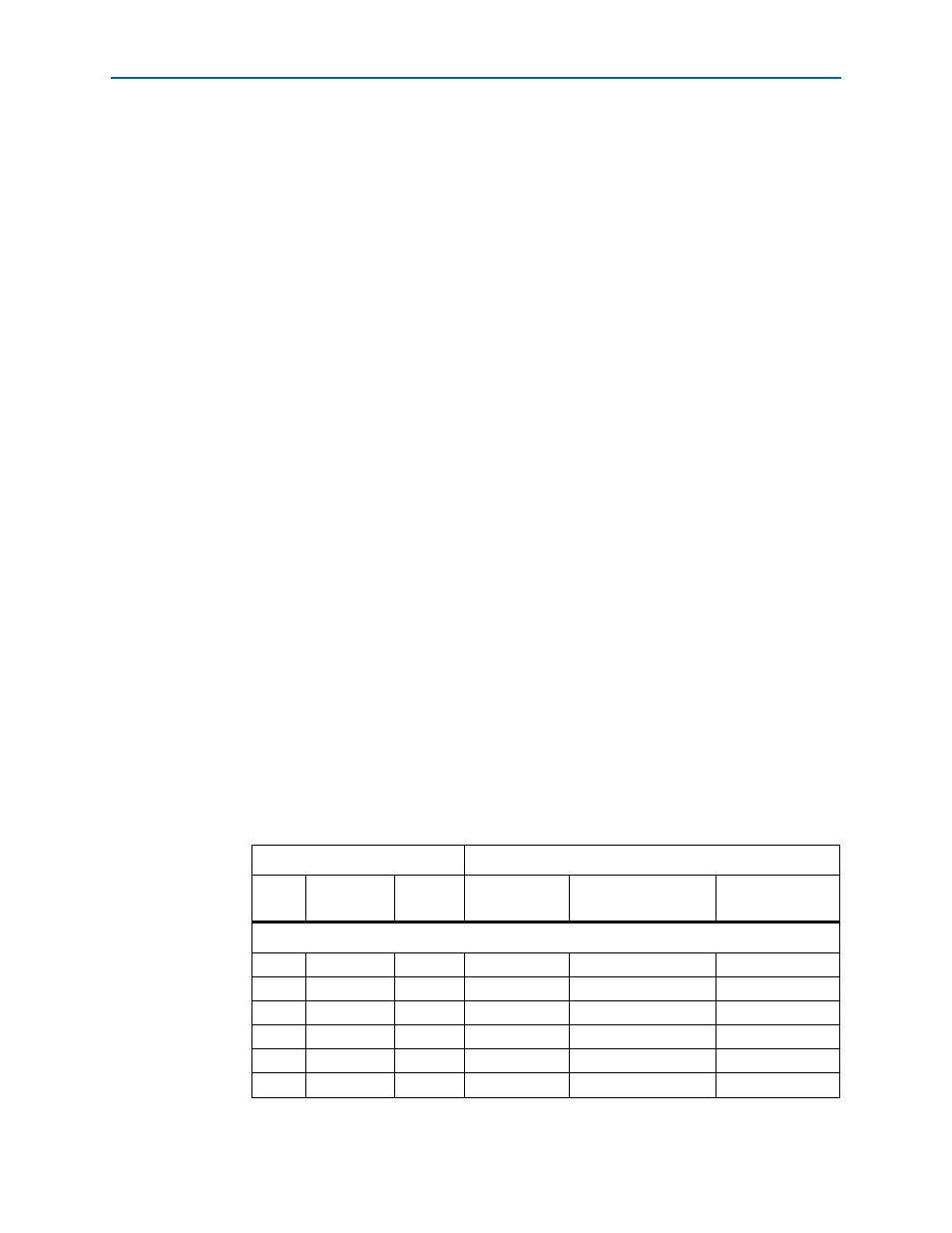

Performance and Resource Utilization

The hard IP implementation of the IP Compiler for PCI Express is available in

Arria II GX, Arria II GZ, Cyclone IV GX, and Stratix IV GX devices.

shows the resource utilization for the hard IP implementation using either

the Avalon-ST or Avalon-MM interface with a maximum payload of 256 bytes and 32

tags for the Avalon-ST interface and 16 tags for the Avalon-MM interface.

Table 1–8. Performance and Resource Utilization in Arria II GX, Arria II GZ, Cyclone IV GX, and

Stratix IV GX Devices (Part 1 of 2)

Parameters

Size

Lane

Width

Internal

Clock (MHz)

Virtual

Channel

Combinational

ALUTs

Dedicated

Registers

Memory Blocks

M9K

Avalon-ST Interface

×1

125

1

100

100

0

×1

125

2

100

100

0

×4

125

1

200

200

0

×4

125

2

200

200

0

×8

250

1

200

200

0

×8

250

2

200

200

0