Altera IP Compiler for PCI Express User Manual

Page 237

Chapter 15: Testbench and Design Example

15–5

Root Port Testbench

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

■

<variation name>_example_rp_pipen1b—This is the example root port design that

includes your variation of the IP core. For more information about this module,

refer to

“Root Port Design Example” on page 15–22

■

altpcietb_bfm_ep_example_chaining_pipen1b

—This is the endpoint PCI

Express model. The EP BFM consists of a Gen2 ×8 IP core endpoint connected to

the chaining DMA design example described in the section

.

shows the parameterization of the

Gen2 ×8 IP core endpoint.

■

altpcietb_pipe_phy

—There are eight instances of this module, one per lane. These

modules connect the PIPE MAC layer interfaces of the root port and the endpoint.

The module mimics the behavior of the PIPE PHY layer to both MAC interfaces.

■

altpcietb_bfm_driver_rp

—This module drives transactions to the root port BFM.

This is the module that you modify to vary the transactions sent to the example

endpoint design or your own design. For more information about this module, see

“Test Driver Module” on page 15–18

.

The testbench has routines that perform the following tasks:

■

Generates the reference clock for the endpoint at the required frequency.

■

Provides a reset at start up.

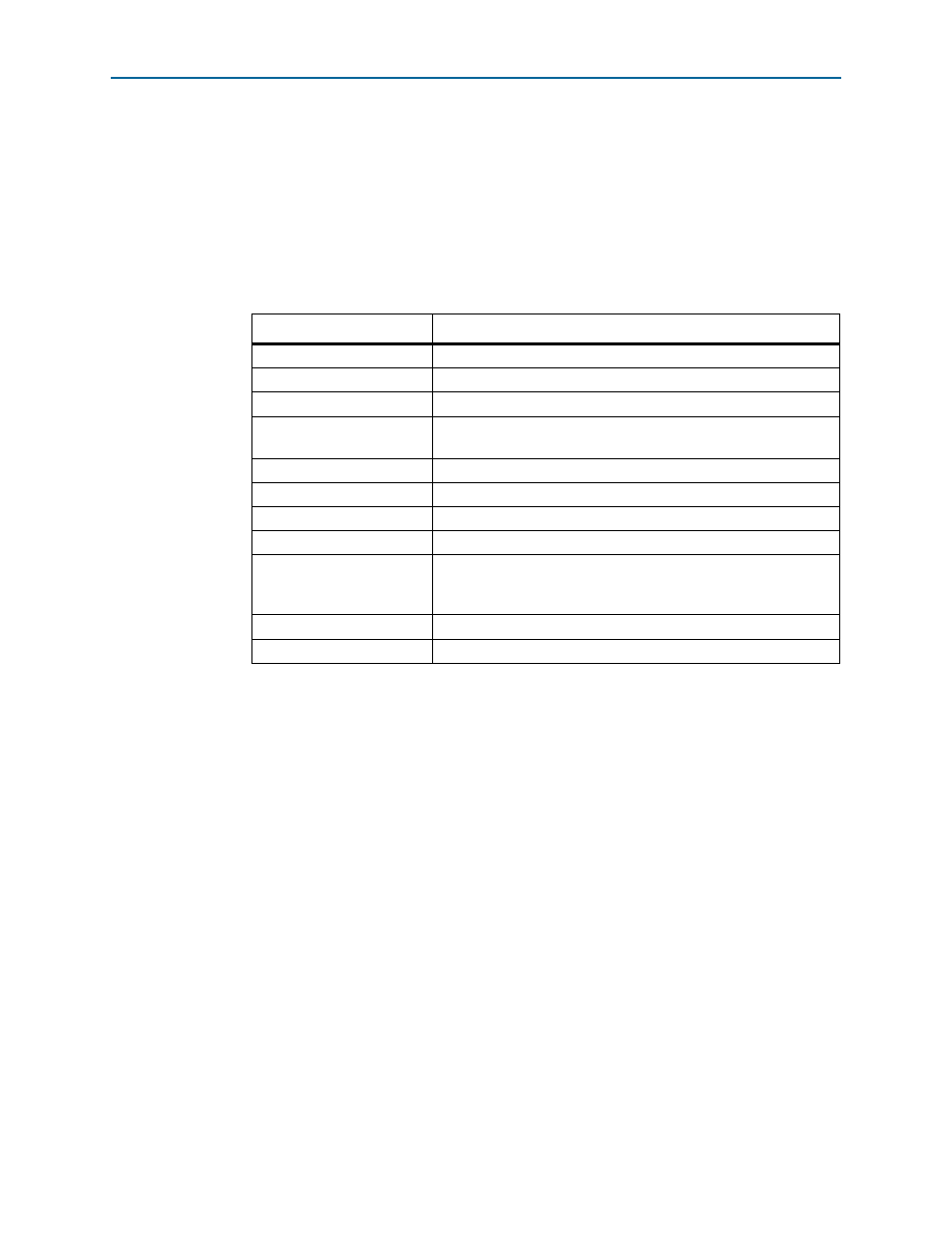

Table 15–2. Gen2 ×8 IP core Endpoint Parameterization

Parameter

Value

Lanes

8

Port Type

Native Endpoint

Max rate

Gen2

BAR Type

BAR1:0—64–bit Prefetchable Memory, 256 MBytes–28 bits

Bar 2:—32–Bit Non-Prefetchable, 256 KBytes–18 bits

Device ID

0xABCD

Vendor ID

0x1172

Tags supported

32

MSI messages requested

4

Error Reporting

Implement ECRC check,

Implement ECRC generations

Implement ECRC generate and forward

Maximum payload size

128 bytes

Number of virtual channels

1