Transaction layer – Altera IP Compiler for PCI Express User Manual

Page 67

Chapter 4: IP Core Architecture

4–9

Transaction Layer

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

shows the block diagram of an IP Compiler for PCI Express with an

Avalon-MM interface.

The PCI Express Avalon-MM bridge provides an interface between the PCI Express

transaction layer and other components across the system interconnect fabric.

Transaction Layer

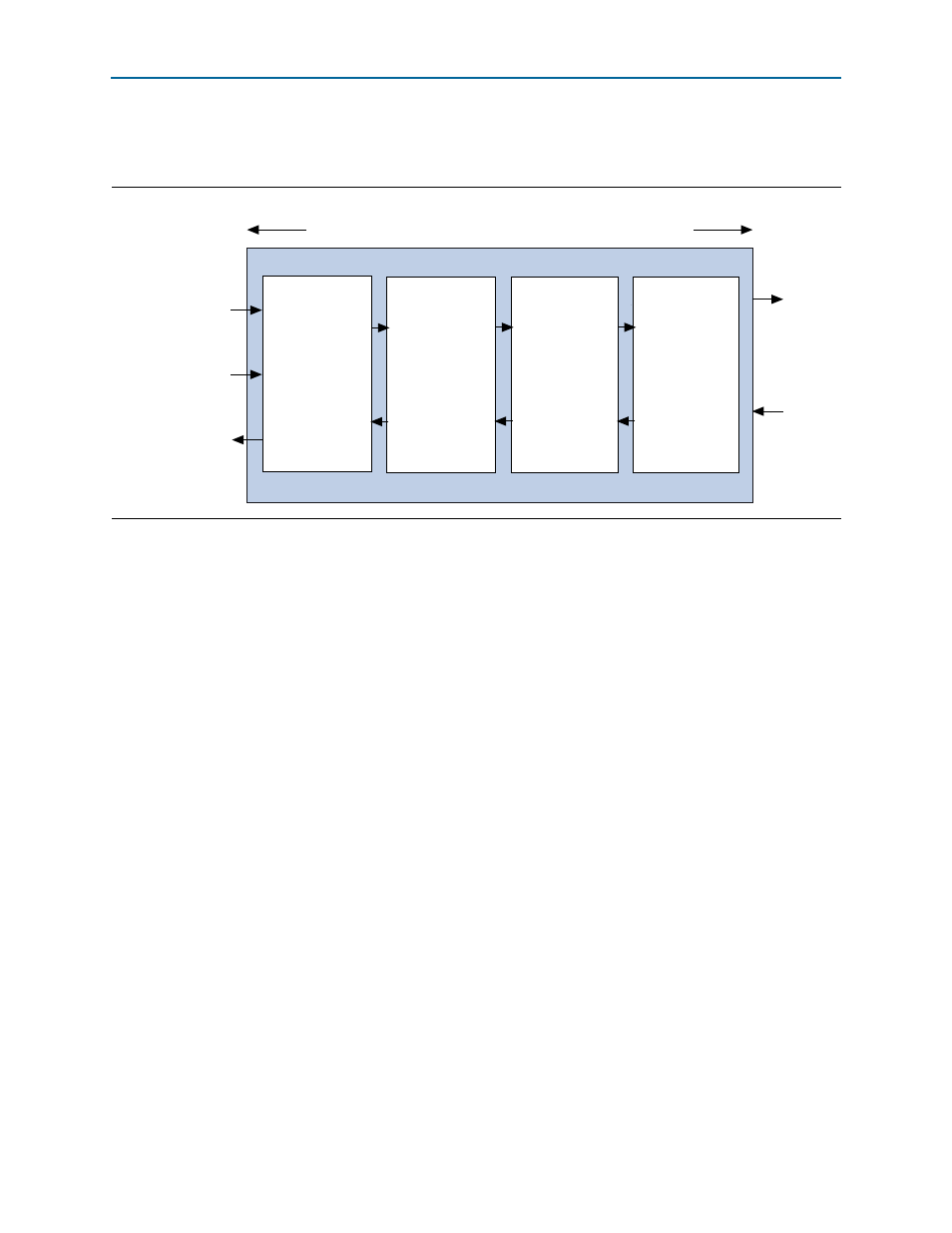

The transaction layer sits between the application layer and the data link layer. It

generates and receives transaction layer packets.

illustrates the transaction

layer of a component with two initialized virtual channels (VCs). The transaction

layer contains three general subblocks: the transmit datapath, the configuration space,

and the receive datapath, which are shown with vertical braces in

.

1

You can parameterize the Stratix IV GX IP core to include one or two virtual channels.

The Arria II GX and Cyclone IV GX implementations include a single virtual channel.

Tracing a transaction through the receive datapath includes the following steps:

1. The transaction layer receives a TLP from the data link layer.

2. The configuration space determines whether the transaction layer packet is well

formed and directs the packet to the appropriate virtual channel based on traffic

class (TC)/virtual channel (VC) mapping.

3. Within each virtual channel, transaction layer packets are stored in a specific part

of the receive buffer depending on the type of transaction (posted, non-posted, or

completion transaction).

4. The transaction layer packet FIFO block stores the address of the buffered

transaction layer packet.

Figure 4–6. IP Compiler for PCI Express with Avalon-MM Interface

Tx

Rx

Transaction Layer

Data Link Layer

Physical Layer

IP Compiler for PCI Express

To Application Layer

To Link

Avalon-MM

Master Port

IP Compiler for PCI Express

Avalon-MM Interface

Avalon-MM

Slave Port

(Control Register

Access)

Avalon-MM

Slave Port

Qsys component

controls the upstream

PCI Express devices.

Qsys component

controls access to

internal control and

status registers.

Root port controls the

downstream Qsys

component.

With information sent

by the application

layer, the transaction

layer generates a TLP,

which includes a

header and, optionally,

a data payload.

The data link layer

ensures packet

integrity, and adds a

sequence number and

link cyclic redundancy

code (LCRC) check to

the packet.

The physical layer

encodes the packet

and transmits it to the

receiving device on the

other side of the link.

The transaction layer

disassembles the

transaction and

transfers data to the

application layer in a

form that it recognizes.

The data link layer

verifies the packet's

sequence number and

checks for errors.

The physical layer

decodes the packet

and transfers it to the

data link layer.