Altera IP Compiler for PCI Express User Manual

Page 83

Chapter 4: IP Core Architecture

4–25

PCI Express Avalon-MM Bridge

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

In Qsys-generated systems, when any interrupt input signal is asserted, the

corresponding bit is written in the

“Avalon-MM to PCI Express Interrupt Status

Register Address: 0x0040” on page 6–7

. Software reads this register and decides

priority on servicing requested interrupts.

After servicing the interrupt, software must clear the appropriate serviced interrupt

status

bit and ensure that no other interrupts are pending. For interrupts caused by

“Avalon-MM to PCI Express Interrupt Status Register Address: 0x0040”

writes, the status bits should be cleared in the

“Avalon-MM to PCI Express Interrupt

Status Register Address: 0x0040”

. For interrupts due to the incoming interrupt

signals on the Avalon-MM interface, the interrupt status should be cleared in the

Avalon-MM component that sourced the interrupt. This sequence prevents interrupt

requests from being lost during interrupt servicing.

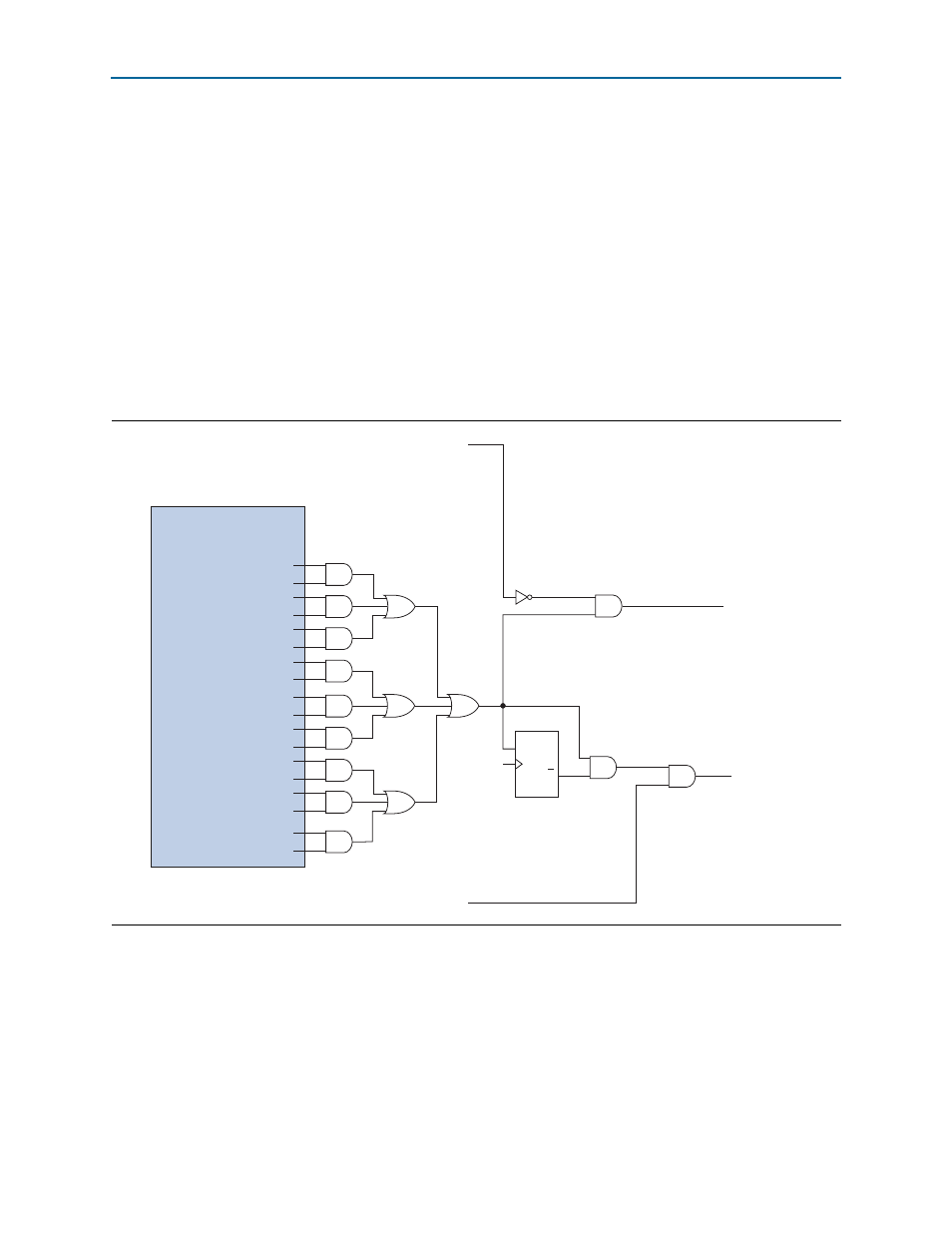

shows the logic for the entire PCI Express interrupt generation process.

The PCI Express Avalon-MM bridge selects either MSI or legacy interrupts

automatically based on the standard interrupt controls in the PCI Express

configuration space registers. The Interrupt Disable bit, which is bit 10 of the

Command

register (at configuration space offset 0x4) can be used to disable legacy

interrupts. The MSI Enable bit, which is bit 0 of the MSI Control Status register in the

MSI capability register (bit 16 at configuration space offset 0x50), can be used to

enable MSI interrupts.

Figure 4–13. IP Compiler for PCI Express Avalon-MM Interrupt Propagation to the PCI Express Link

SET

CLR

D

Q

Q

Interrupt Disable

(Configuration Space Command Register [10])

Avalon-MM-to-PCI-Express

Interrupt Status and Interrupt

Enable Register Bits

A2P_MAILBOX_INT7

A2P_MB_IRQ7

A2P_MAILBOX_INT6

A2P_MB_IRQ6

A2P_MAILBOX_INT5

A2P_MB_IRQ5

A2P_MAILBOX_INT4

A2P_MB_IRQ4

A2P_MAILBOX_INT3

A2P_MB_IRQ3

A2P_MAILBOX_INT2

A2P_MB_IRQ2

A2P_MAILBOX_INT1

A2P_MB_IRQ1

A2P_MAILBOX_INT0

A2P_MB_IRQ0

AV_IRQ_ASSERTED

AVL_IRQ

MSI Enable

(Configuration Space Message Control Register[0])

MSI Request

PCI Express Virtual INTA signalling

(When signal rises ASSERT_INTA Message Sent)

(When signal falls DEASSERT_INTA Message Sent)