Ecc error signals, Pci express interrupts for endpoints – Altera IP Compiler for PCI Express User Manual

Page 113

Chapter 5: IP Core Interfaces

5–27

Avalon-ST Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

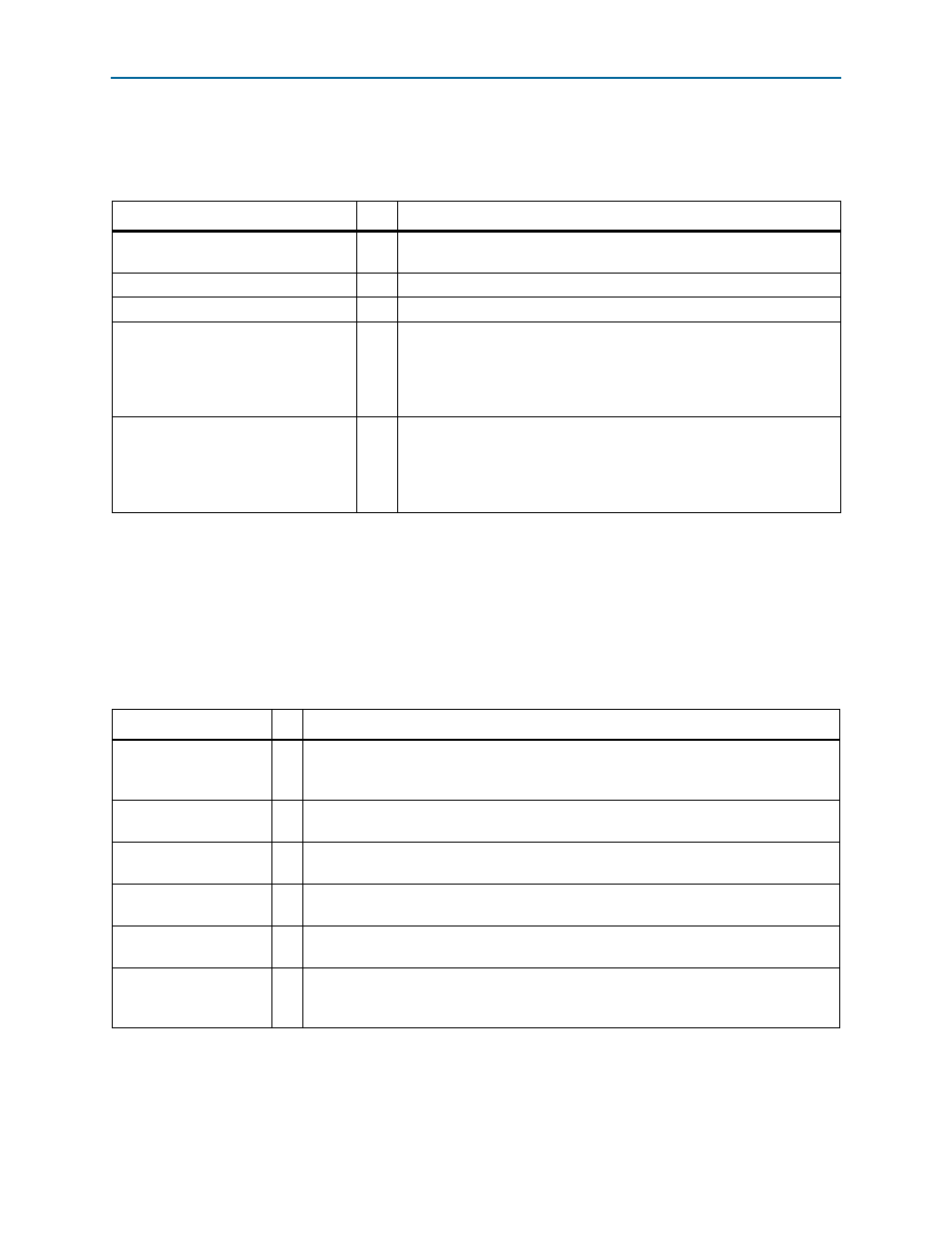

ECC Error Signals

shows the ECC error signals for the hard IP implementation.

PCI Express Interrupts for Endpoints

describes the IP core’s interrupt signals for endpoints.

Table 5–8. ECC Error Signals for Hard IP Implementation

Signal

I/O

Description

derr_cor_ext_rcv[1:0]

O

Indicates a correctable error in the RX buffer for the corresponding virtual

channel.

derr_rpl

O

Indicates an uncorrectable error in the retry buffer.

derr_cor_ext_rpl

O

Indicates a correctable error in the retry buffer.

r2c_err0

O

Indicates an uncorrectable ECC error on VC0. Altera recommends

resetting the IP Compiler for PCI Express when an uncorrectable ECC error

is detected and the packet cannot be terminated early. Resetting

guarantees that the Configuration Space Registers are not corrupted by an

errant TLP.

r2c_err1

O

Indicates an uncorrectable ECC error on VC1. Altera recommends

reseeting the IP Compiler for PCI Express when an uncorrectable ECC

error is detected and the packet cannot be terminated early. Resetting

guarantees that the Configuration Space Registers are not corrupted by an

errant TLP

Notes to

(1) These signals are not available for the hard IP implementation in Arria II GX devices.

(2) The Avalon-ST rx_st_err<n> described in

indicates an uncorrectable error in the RX buffer.

(3) This signal applies only when ECC is enabled in some hard IP configurations. Refer to

Table 5–9. Interrupt Signals for Endpoints (Part 1 of 2)

Signal

I/O

Description

app_msi_req

I

Application MSI request. Assertion causes an MSI posted write TLP to be generated based

on the MSI configuration register values and the app_msi_tc and app_msi_num input

ports.

app_msi_ack

O

Application MSI acknowledge. This signal is sent by the IP core to acknowledge the

application's request for an MSI interrupt.

app_msi_tc[2:0]

I

Application MSI traffic class. This signal indicates the traffic class used to send the MSI

(unlike INTX interrupts, any traffic class can be used to send MSIs).

app_msi_num[4:0]

I

Application MSI offset number. This signal is used by the application to indicate the offset

between the base message data and the MSI to send.

cfg_msicsr[15:0]

O

Configuration MSI control status register. This bus provides MSI software control. Refer to

for more information.

pex_msi_num[4:0]

I

Power management MSI number. This signal is used by power management and hot plug

to determine the offset between the base message interrupt number and the message

interrupt number to send through MSI.