Avalon-mm configuration – Altera IP Compiler for PCI Express User Manual

Page 56

3–20

Chapter 3: Parameter Settings

IP Core Parameters

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

Avalon-MM Configuration

The Avalon Configuration page contains parameter settings for the PCI Express

Avalon-MM bridge. The bridge is available only in the Qsys design flow.For more

information about the Avalon-MM configuration parameters in the Qsys design flow,

refer to

“Parameters in the Qsys Design Flow” on page 3–1

.

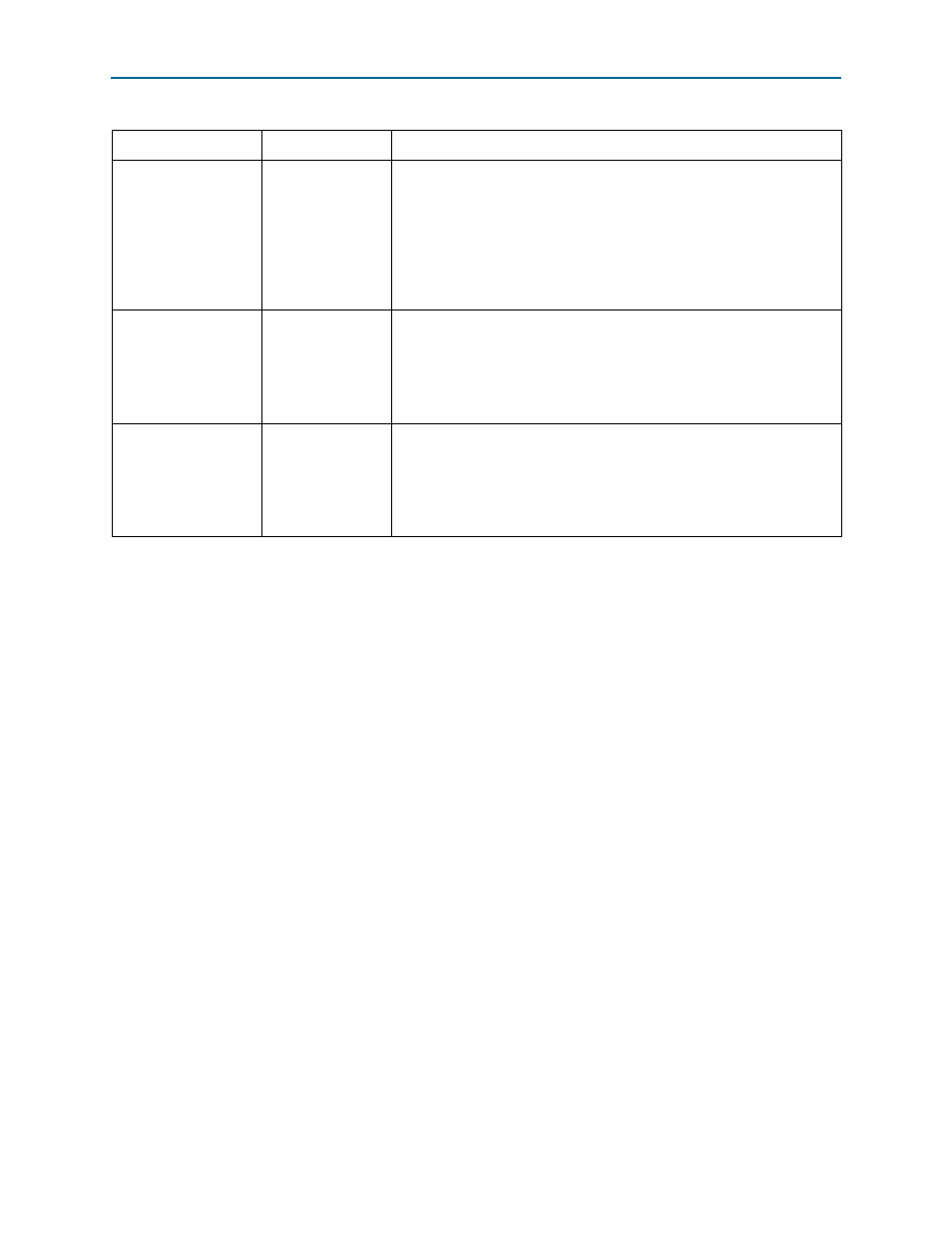

Endpoint L1

acceptable latency

< 1 µs to > 64 µs

This value indicates the acceptable latency that an endpoint can withstand

in the transition from the L1 to L0 state. It is an indirect measure of the

endpoint’s internal buffering. This setting is disabled for root ports. Sets the

read-only value of the endpoint L1 acceptable latency field of the device

capabilities register. It provides information to other devices which have

turned On the Enable L1 ASPM option. If you select the Arria GX,

Arria II GX, Cyclone IV GX, Stratix II GX, or Stratix IV GX PHY, this option

is turned off and disabled.

L1 Exit Latency

Common clock

< 1µs to > 64 µs

Indicates the L1 exit latency for the separate clock. Used to calculate the

value of the L1 exit latency field of the device capabilities register (0x084). If

you select the Arria GX, Arria II GX, Cyclone IV GX, Stratix II GX, or

Stratix IV GX PHY this parameter is disabled and set to its maximum value.

If you are using an external PHY, consult the PHY vendor's documentation

to determine the correct value for this parameter.

L1 Exit Latency

Separate clock

< 1µs to > 64 µs

Indicates the L1 exit latency for the common clock. Used to calculate the

value of the L1 exit latency field of the device capabilities register (0x084). If

you select the Arria GX, Arria II GX, Cyclone IV GX, Stratix II GX, or

Stratix IV GX PHY, this parameter is disabled and set to its maximum value.

If you are using an external PHY, consult the PHY vendor's documentation

to determine the correct value for this parameter.

Table 3–13. Power Management Parameters (Part 2 of 2)

Parameter

Value

Description