Shmem_fill procedure, Shmem_chk_ok function – Altera IP Compiler for PCI Express User Manual

Page 274

15–42

Chapter 15: Testbench and Design Example

BFM Procedures and Functions

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

shmem_display VHDL Procedure or Verilog HDL Function

The shmem_display VHDL procedure or Verilog HDL function displays a block of

data from the BFM shared memory.

shmem_fill Procedure

The shmem_fill procedure fills a block of BFM shared memory with a specified data

pattern.

shmem_chk_ok Function

The shmem_chk_ok function checks a block of BFM shared memory against a specified

data pattern.

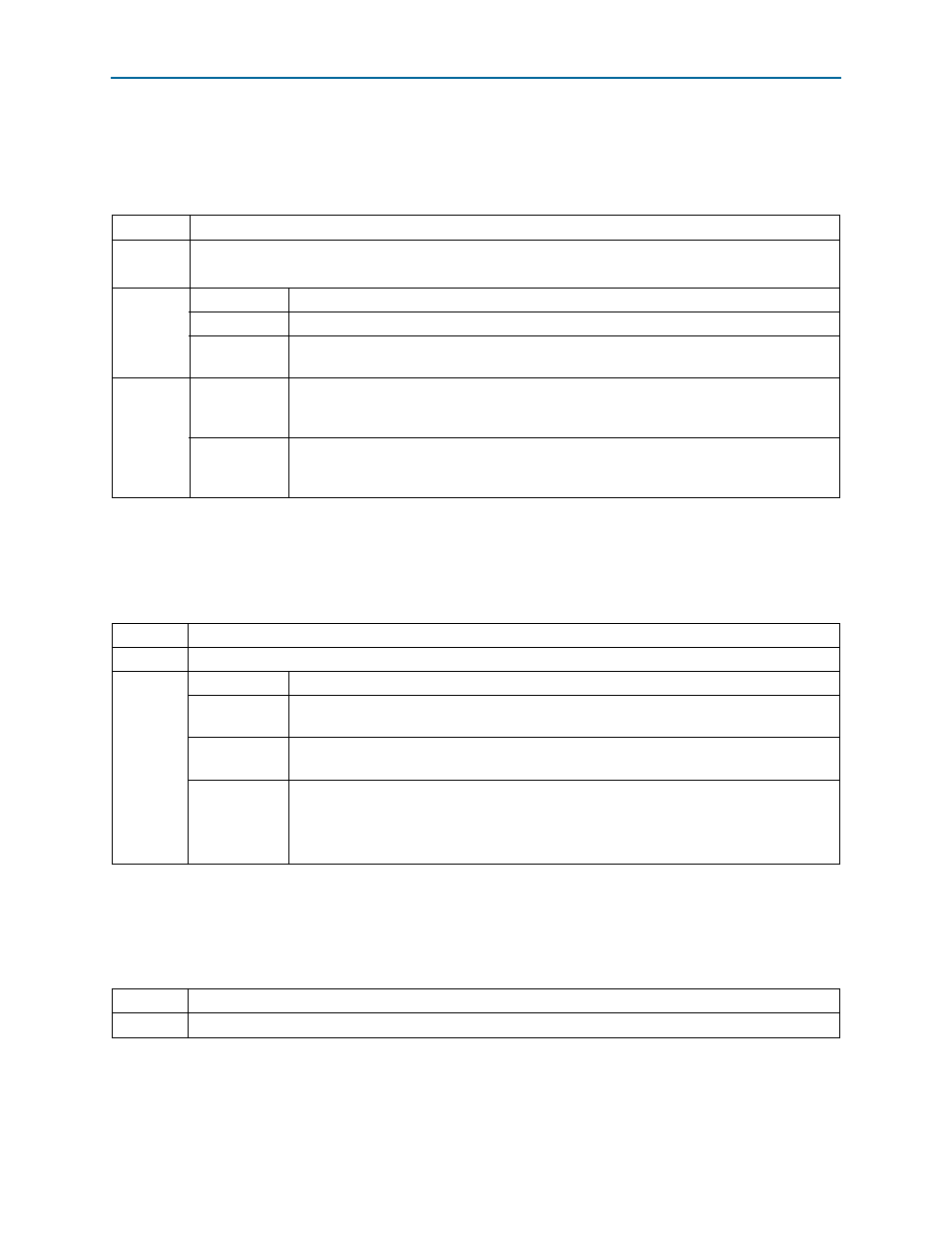

Table 15–36. shmem_display VHDL Procedure/ or Verilog Function

Location

altpcietb_bfm_shmem.v or altpcietb_bfm_shmem.vhd

Syntax

VHDL: shmem_display(addr, leng, word_size, flag_addr, msg_type)

Verilog HDL: dummy_return:=shmem_display(addr, leng, word_size, flag_addr, msg_type);

Arguments addr

BFM shared memory starting address for displaying data.

leng

Length, in bytes, of data to display.

word_size

Size of the words to display. Groups individual bytes into words. Valid values are 1, 2, 4, and

8.

flag_addr

Adds a <== flag to the end of the display line containing this address. Useful for marking

specific data. Set to a value greater than 2**21 (size of BFM shared memory) to suppress the

flag.

msg_type

Specifies the message type to be displayed at the beginning of each line. See

Message Procedures” on page 15–43

for more information about message types. Set to one

of the constants defined in

Table 15–37. shmem_fill Procedure

Location

altpcietb_bfm_shmem.v or altpcietb_bfm_shmem.vhd

Syntax

shmem_fill(addr, mode, leng, init)

Arguments addr

BFM shared memory starting address for filling data.

mode

Data pattern used for filling the data. Should be one of the constants defined in section

“Shared Memory Constants” on page 15–41

.

leng

Length, in bytes, of data to fill. If the length is not a multiple of the incrementing data pattern

width, then the last data pattern is truncated to fit.

init

Initial data value used for incrementing data pattern modes In VHDL. This argument is type

std_logic_vector(63 downto 0). In Verilog HDL, this argument is reg [63:0].

In both languages, the necessary least significant bits are used for the data patterns that are

smaller than 64 bits.

Table 15–38. shmem_chk_ok Function (Part 1 of 2)

Location

altpcietb_bfm_shmem.v or altpcietb_bfm_shmem.vhd

Syntax

result:= shmem_chk_ok(addr, mode, leng, init, display_error)