Compiling the design, Programming a device – Altera IP Compiler for PCI Express User Manual

Page 307

Chapter 16: Qsys Design Example

16–19

Compiling the Design

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

8. In the Settings window, in the Category panel, click Libraries.

9. Under Project libraries, browse to add the directories listed in

10. Click Apply.

11. Click OK.

Compiling the Design

Follow these steps to compile your design:

1. In the Quartus II software, open the s4gx_gen1x8_qsys_top.qpf project if it is not

already open

2. On the Processing menu, click Start Compilation.

3. After compilation, expand the TimeQuest Timing Analyzer folder in the

Compilation Report. Note whether the timing constraints are achieved in the

Compilation Report.

If your design does not initially meet the timing constraints, you can find the

optimal Fitter settings for your design by using the Design Space Explorer. To use

the Design Space Explorer,on the Tools menu, click Launch Design Space

Explorer

.

Programming a Device

After you compile your design, you can program your targeted Altera device and

verify your design in hardware.

f

For information about programming a device, refer to the

in volume 3 of the Quartus II Handbook.

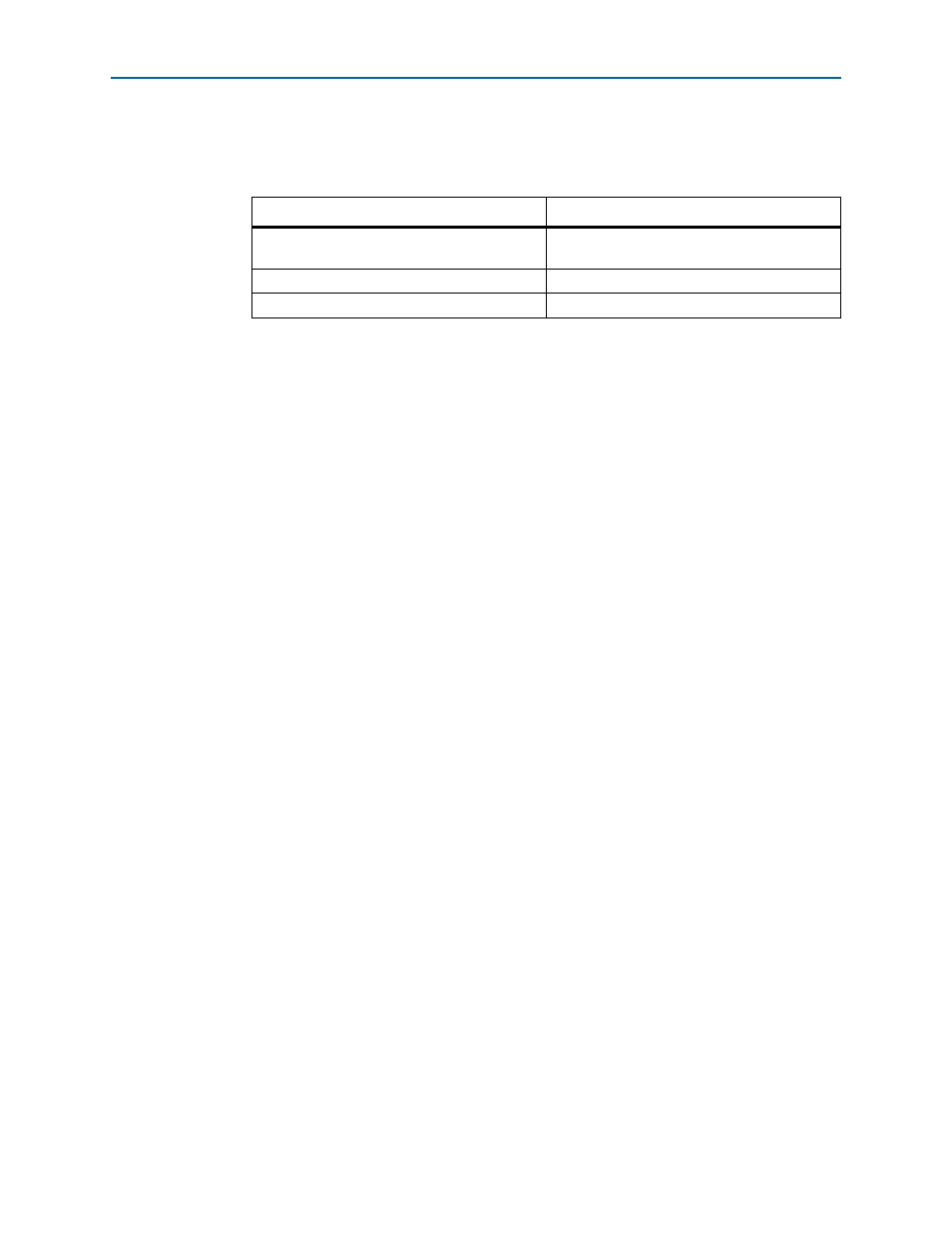

Table 16–14. Library Search Paths

Directory Path

Description

<project directory>

Current project directory for project top-level

file, altgxb_reconfig file, and PLL file.

hip_s4gx_gen1x8_qsys/synthesis

Path to Qsys top level files.

hip_s4gx_gen1x8_qsys/synthesis/submodules

Path to other modules in the design.