Clock signals, Reset and status signals – Altera IP Compiler for PCI Express User Manual

Page 137

Chapter 5: IP Core Interfaces

5–51

Avalon-MM Application Interface

August 2014

Altera Corporation

IP Compiler for PCI Express User Guide

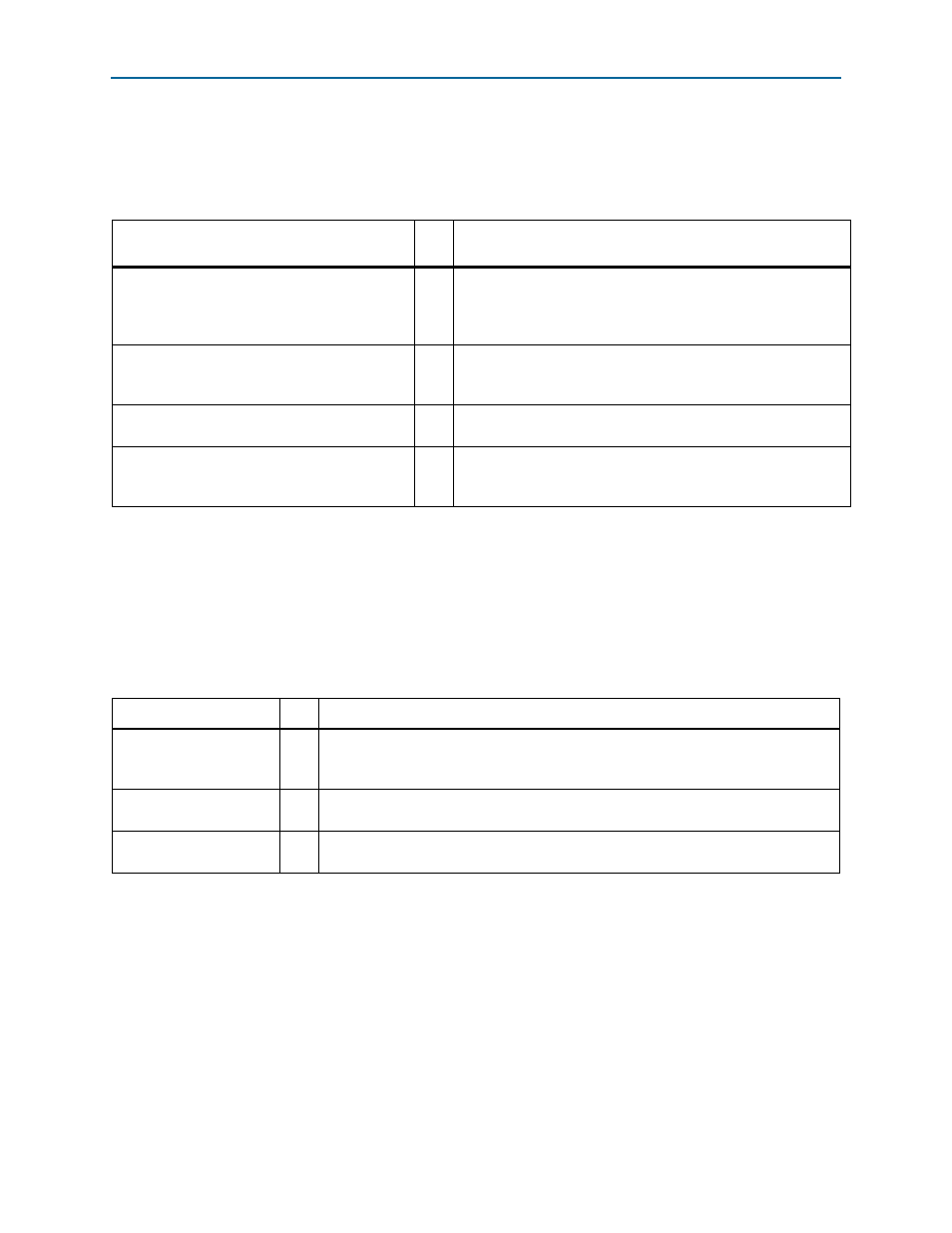

Clock Signals

describes the clock signals for IP Compiler for PCI Express variations

generated in Qsys.

Refer to

“Avalon-MM Interface–Hard IP and Soft IP Implementations” on page 7–11

for a complete explanation of the clocking scheme.

Reset and Status Signals

describes the reset and status signals for IP Compiler for PCI Express

variations generated in Qsys.

Table 5–26. Avalon-MM Clock Signals

Signal Name in

Qsys

I/O

Description

refclk/refclk_export

I

An external clock source. When you turn on the Use separate

clock option on the Avalon Configuration page, the PCI Express

protocol layers are driven by an internal clock that is generated

from refclk. This option is not available in Qsys.

clk125_out/pcie_core_clk

O

This clock is exported by the IP Compiler for PCI Express. It can be

used for logic outside of the IP core. It is not visible and cannot be

used to drive other Avalon-MM components in the system.

pcie_core_reset_reset_n

(Qsys only)

O

This is the reset signal for the pcie_core_clk_clk domain in

Qsys.

AvlClk_i/

not available

I

Avalon-MM global clock. clk connects to AvlClk_i which is the

main clock source of the system. clk is user-specified. It can be

generated on the PCB or derived from other logic in the system.

Table 5–27. Avalon-MM Reset and Status Signals

Signal

I/O

Description

pcie_rstn/

pcie_rstn_export

I

Pcie_rstn

directly resets all sticky IP Compiler for PCI Express configuration registers

through the npor input. Sticky registers are those registers that fail to reset in L2 low

power mode or upon a fundamental reset.

reset_n/

avalon_reset

I

reset_n

is the system-wide reset which resets all PCI Express IP core circuitry not

affected by pcie_rstn/pcie_rstn_export.

suc_spd_neg/

suc_spd_neg

O

suc_spd_neg

is a status signal which Indicates successful speed negotiation to Gen2

when asserted.