Root port mode configuration requests, Ecrc forwarding – Altera IP Compiler for PCI Express User Manual

Page 108

5–22

Chapter 5: IP Core Interfaces

Avalon-ST Interface

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

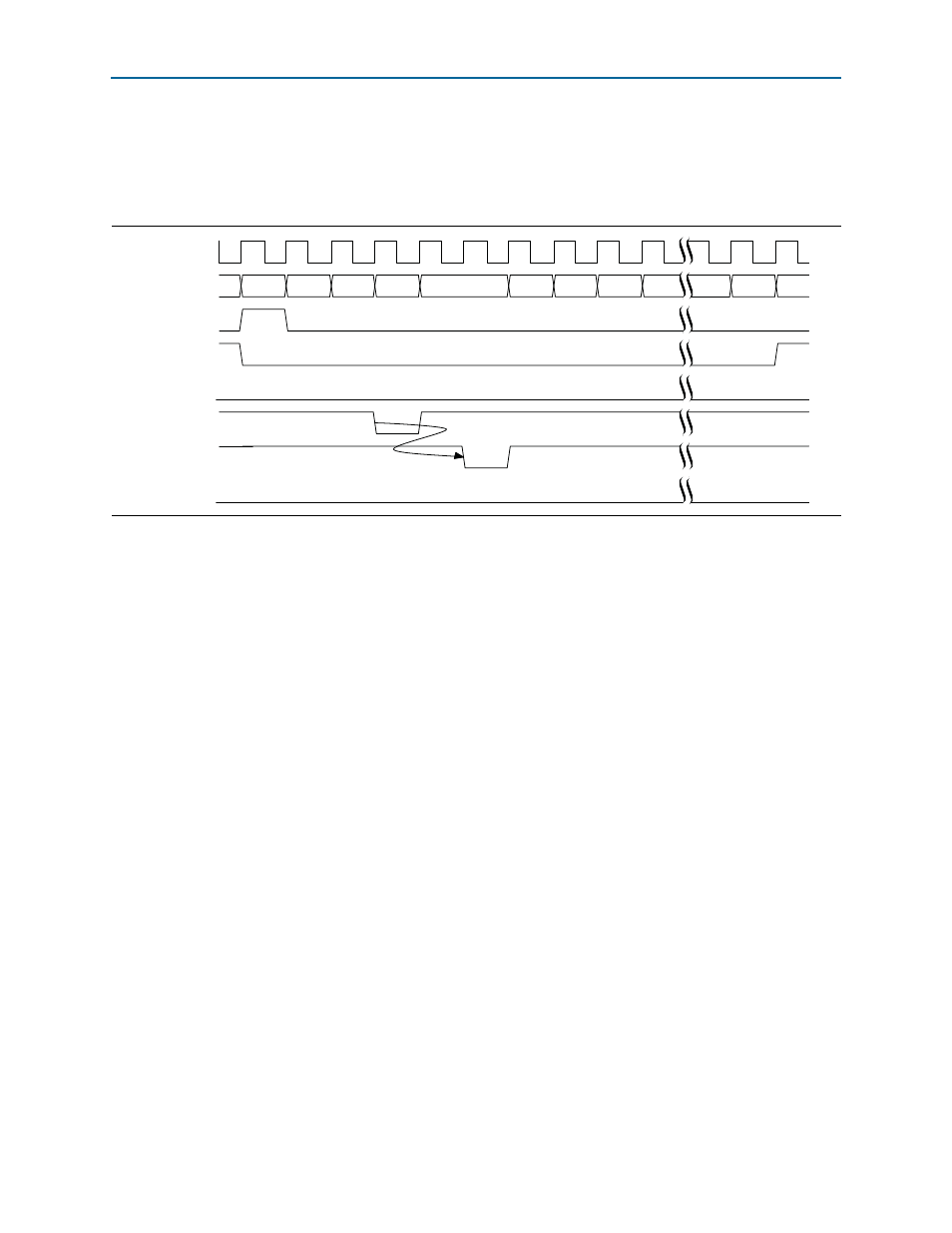

illustrates the timing of the 128-bit TX interface when the IP Compiler for

PCI Express backpressures the application by deasserting tx_st_ready. Because the

readyLatency

is two cycles, the application deasserts tx_st_valid after two cycles

and holds tx_st_data until two cycles after tx_st_ready is reasserted

Root Port Mode Configuration Requests

To ensure proper operation when sending CFG0 transactions in root port mode, the

application should wait for the CFG0 to be transferred to the IP core’s configuration

space before issuing another packet on the Avalon-ST TX port. You can do this by

waiting at least 10 clocks from the time the CFG0 SOP is issued on Avalon-ST and

then checking for tx_fifo_empty0==1 before sending the next packet.

If your application implements ECRC forwarding, it should not apply ECRC

forwarding to CFG0 packets that it issues on Avalon-ST. There should be no ECRC

appended to the TLP, and the TD bit in the TLP header should be set to 0. These

packets are internally consumed by the IP core and are not transmitted on the PCI

Express link.

ECRC Forwarding

On the Avalon-ST interface, the ECRC field follows the same alignment rules as

payload data. For packets with payload, the ECRC is appended to the data as an extra

dword of payload. For packets without payload, the ECRC field follows the address

alignment as if it were a one dword payload. Depending on the address alignment,

through

the ECRC data for RX data.

illustrate the position of ECRC data for TX data. For packets with no

payload data, the ECRC would correspond to Data0 in these figures.

Figure 5–26. 128-Bit Transaction Layer Backpressures the Application

clk

tx_st_data[127:0]

tx_st_sop

tx_st_eop

tx_st_empty

tx_st_ready

tx_st_valid

tx_st_err

.. 000

. CC

. CC

. CC

. CCCC021

. CC

. CC

. CC

. CC

. CC

. CC

. CC

.