0x800, 0x834 – Altera IP Compiler for PCI Express User Manual

Page 154

6–6

Chapter 6: Register Descriptions

PCI Express Avalon-MM Bridge Control Register Content

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

describes the PCI Express advanced error reporting extended capability

structure.

PCI Express Avalon-MM Bridge Control Register Content

Control and status registers in the PCI Express Avalon-MM bridge are implemented

in the CRA slave module. The control registers are accessible through the Avalon-MM

slave port of the CRA slave module. This module is optional; however, you must

include it to access the registers.

The control and status register space is 16KBytes. Each 4 KByte sub-region contains a

specific set of functions, which may be specific to accesses from the PCI Express root

complex only, from Avalon-MM processors only, or from both types of processors.

Because all accesses come across the system interconnect fabric —requests from the IP

Compiler for PCI Express are routed through the interconnect fabric— hardware does

not enforce restrictions to limit individual processor access to specific regions.

However, the regions are designed to enable straight-forward enforcement by

processor software.

0x168

VC Resource Control Register (7)

Note to

(1) Refer to

for a comprehensive list of correspondences between the configuration space

registers and the

Table 6–9. Virtual Channel Capability Structure, Rev2 Spec: Virtual Channel Capability (Part 2 of 2)

Byte Offset

31:24

23:16

15:8

7:0

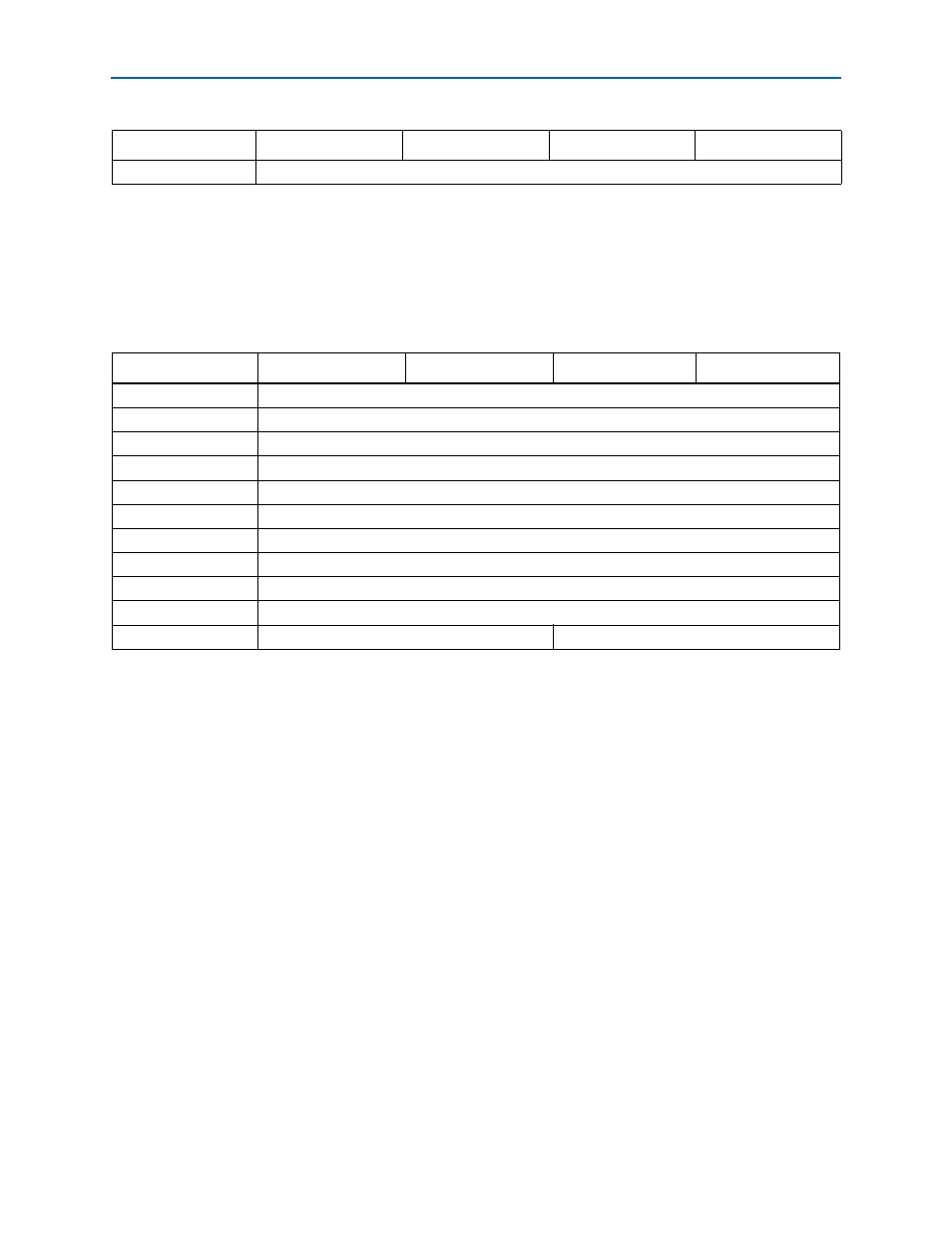

Table 6–10. PCI Express Advanced Error Reporting Extended Capability Structure, Rev2 Spec: Advanced Error Reporting

Capability

Byte Offset

31:24

23:16

15:8

7:0

0x800

PCI Express Enhanced Capability Header

0x804

Uncorrectable Error Status Register

0x808

Uncorrectable Error Mask Register

0x80C

Uncorrectable Error Severity Register

0x810

Correctable Error Status Register

0x814

Correctable Error Mask Register

0x818

Advanced Error Capabilities and Control Register

0x81C

Header Log Register

0x82C

Root Error Command

0x830

Root Error Status

0x834

Error Source Identification Register

Correctable Error Source ID Register

Note to

:

(1) Refer to

for a comprehensive list of correspondences between the configuration space registers and the