Parameterizing the ip compiler for pci express – Altera IP Compiler for PCI Express User Manual

Page 292

16–4

Chapter 16: Qsys Design Example

Parameterizing the IP Compiler for PCI Express

IP Compiler for PCI Express User Guide

August 2014

Altera Corporation

f

Refer to

me 1 of the Quartus II Handbook for more

information about how to use Qsys, including information about the Project Settings

tab. For an explanation of each Qsys menu item, refer

Quartus II

Help.

3. To name your Qsys system, follow these steps:

a. On the File menu, click Save.

b. Under File name, type hip_s4gx_gen1x8_qsys.

c. Click Save. The Qsys system is saved in the new file

hip_s4gx_gen1x8_qsys.qsys

in your project directory.

1

This example design requires that you not specify the same name for the Qsys system

as for the top-level project file, because you must configure additional blocks in your

system that are not available as Qsys components. Later, you create a wrapper HDL

file of the same name as the project and instantiate the generated Qsys system and

these additional blocks in the wrapper HDL file.

4. To remove the default clock clk_0 from the Qsys system, in the System Contents

tab, highlight the component and click the red X on the left edge of the System

Contents

tab. All modules in your synchronous design use the IP Compiler for

PCI Express core clock.

5. To add the IP Compiler for PCI Express component to your system, from the

System Contents

tab, under Interface Protocols in the PCI folder, double-click the

IP Compiler for PCI Express

component. The IP Compiler for PCI Express

parameter editor appears.

Parameterizing the IP Compiler for PCI Express

Bold headings in the IP Compiler for PCI Express parameter editor divide the

parameter list into separate sections. You can use the scroll bar on the right to view

parameters that are not initially visible. To parameterize the IP Compiler for PCI

Express, follow these steps:

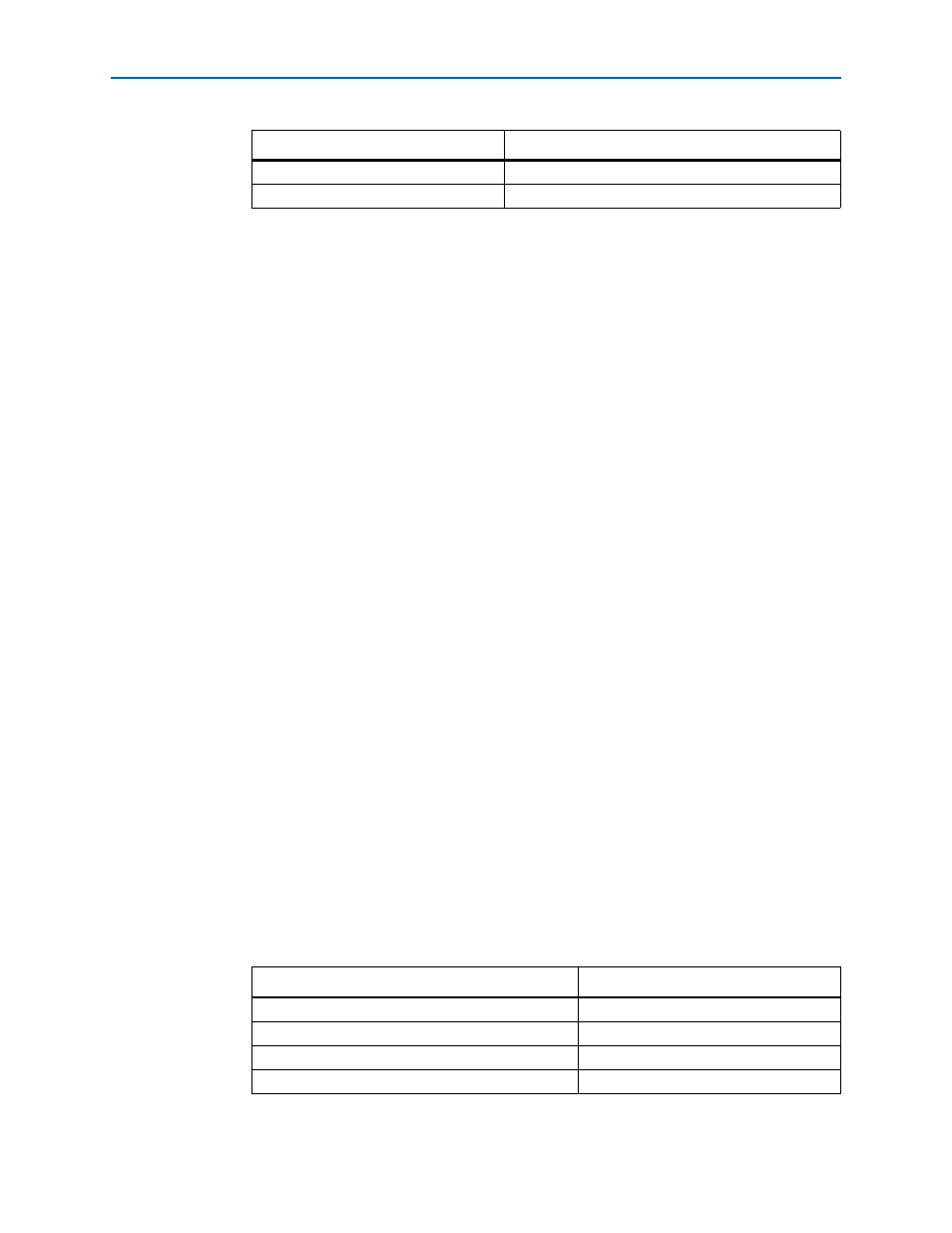

1. Under the System Settings heading, specify the settings in

.

Limit interconnect pipeline stages to

2

Generation ID

0

Table 16–1. Project Settings

Parameter

Value

Table 16–2. IP Compiler for PCI Express System Settings (Part 1 of 2)

Parameter

Value

Device Family

Stratix IV GX

Gen2 Lane Rate Mode

Leave this option off

Number of Lanes

×8

Reference clock frequency

100 MHz