Chapter 6 systemverilog tutorials, Verifying a slave dut – Altera Mentor Verification IP Altera Edition AMBA AXI3/4TM User Manual

Page 155

Mentor VIP AE AXI3/4 User Guide, V10.2b

137

September 2013

Chapter 6

SystemVerilog Tutorials

This chapter discusses how to use the Mentor Verification IP Altera Edition master and slave

BFMs to verify slave and master DUT components.

tutorial the slave is an on-chip RAM model that is verified using

a master BFM and test program.

tutorial the master issues simple write and read transactions that

are verified using a slave BFM and test program.

Following this top-level discussion of how you verify a master and a slave component using the

Mentor Verification IP Altera Edition is a brief example of how to run Qsys, the powerful

system integration tool in Quartus

®

II software. This procedure shows you how to use Qsys to

create a top-level DUT environment. For more details on this example, refer to

Verifying a Slave DUT

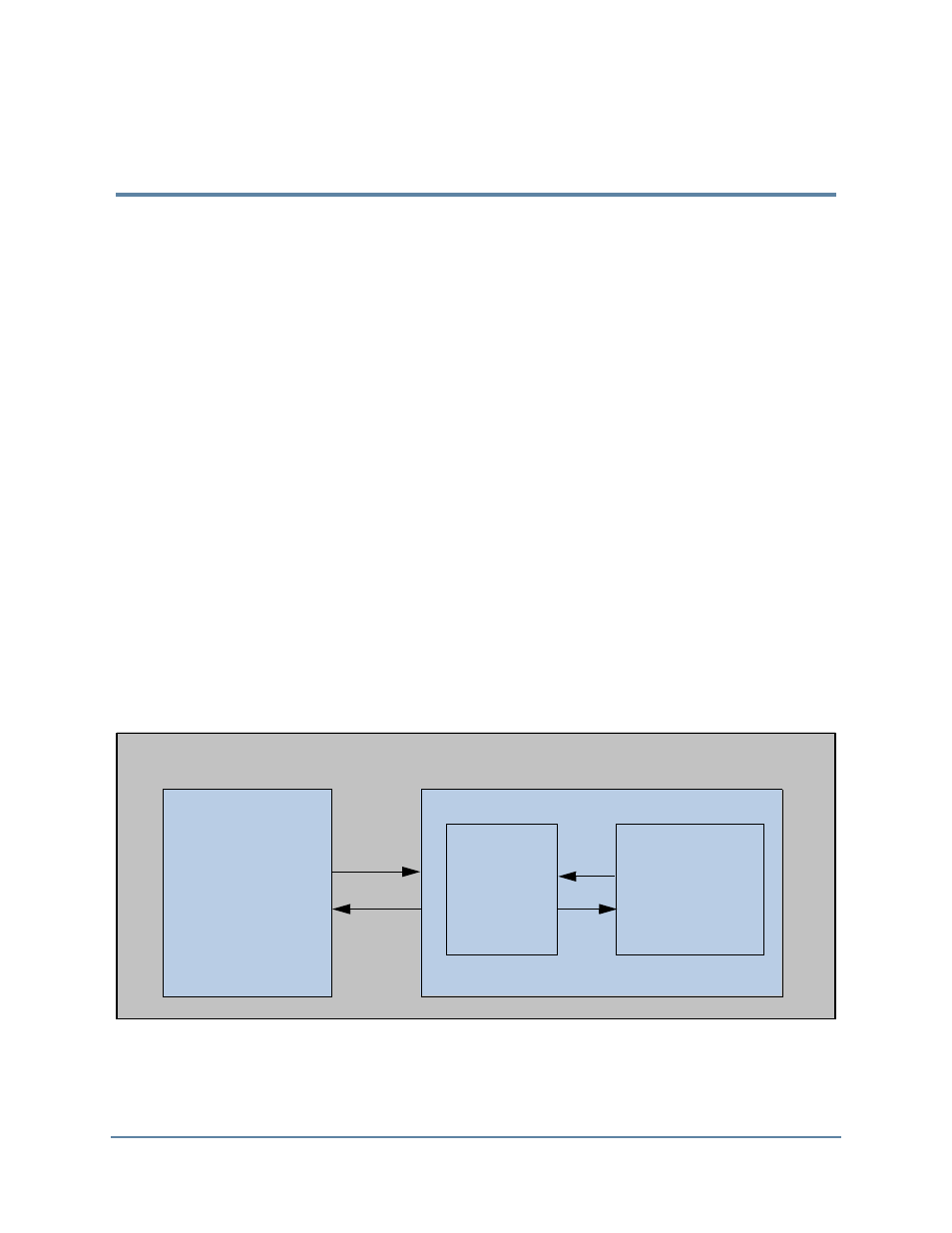

A slave DUT component is connected to a master BFM at the signal-level. A master test

program, written at the transaction-level, generates stimulus via the master BFM to verify the

slave DUT.

illustrates a typical top-level testbench environment.

Figure 6-1. Slave DUT Top-level Testbench Environment

In this example the master test program also compares the written data with that read back from

the slave DUT, reporting the result of the comparison.

Program

Test

Master

BFM

On-chip

RAM Slave

Master

Top-level File