Operation mode, For example, figure, Figure 7-2 – Altera Mentor Verification IP Altera Edition AMBA AXI3/4TM User Manual

Page 216

Mentor VIP AE AXI3/4 User Guide, V10.2b

198

VHDL API Overview

Operational Transaction Fields

September 2013

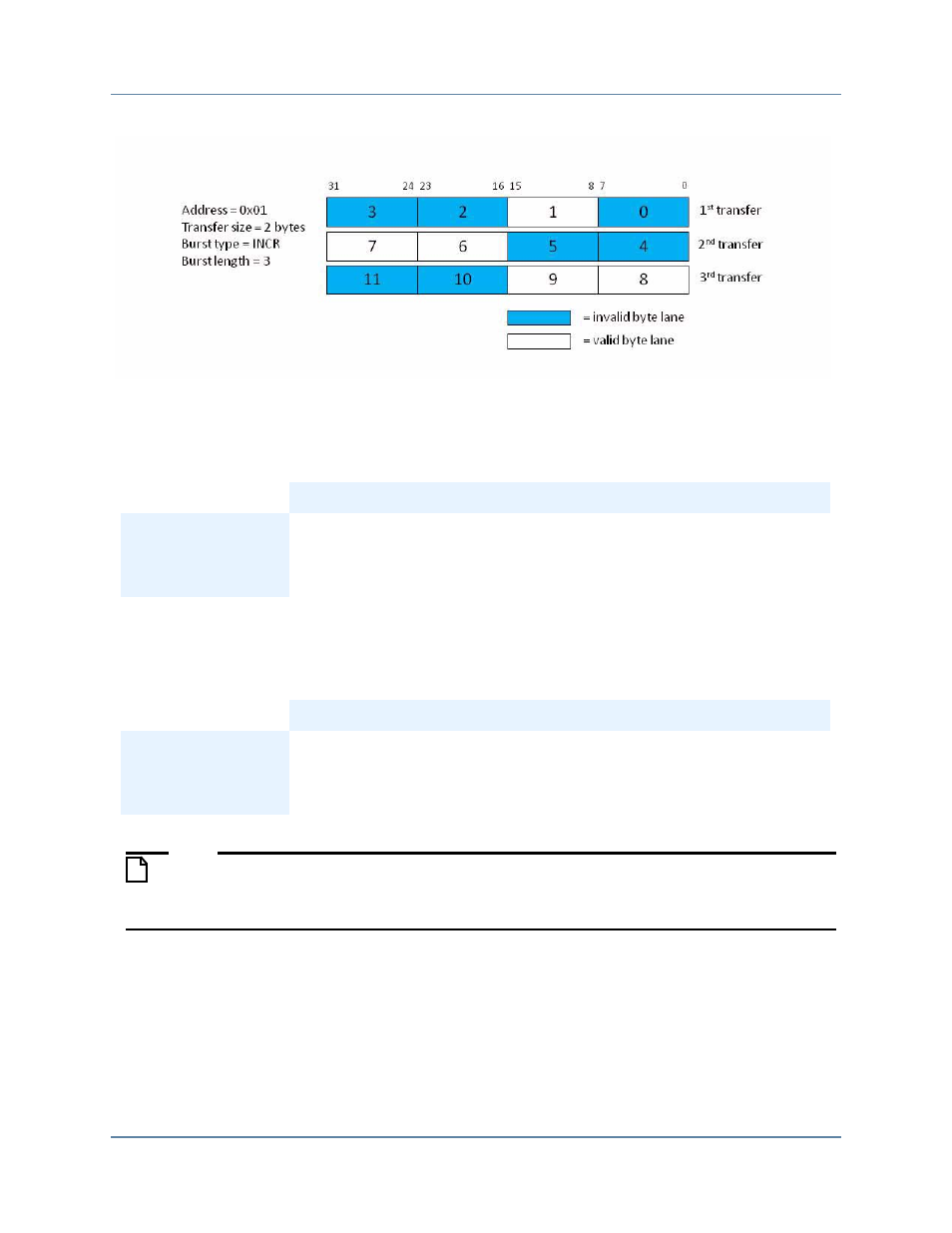

Figure 7-2. Valid Data on Byte Lanes During a Write Transaction

In the above example, if you set all write_strobes[] array elements to 1 prior to executing the

write transaction, automatic correction produces the following results during execution of the

transaction.

If you randomly set all write_strobes[] array elements to 0 or 1, prior to executing the write

transaction, automatic correction only corrects those write_strobes[] array elements that were

previously set to 1, as shown below.

Note

To automatically generate all WSTRB signals for a write transaction, set all

write_strobes[] array elements to 1 prior to execution of the write transaction or write

data burst.

Operation Mode

By default, each read or write transaction performs a blocking operation which prevents a

following transaction from starting until the current active transaction completes.

Prior to Execution

During Execution

1st data phase

write_strobes[0]=0b1111

->

write_strobes[0]=0b0010

2nd data phase

write_strobes[1]=0b1111

->

write_strobes[1]=0b1100

3rd data phase

write_strobes[2]=0b1111

->

write_strobes[2]=0b0011

Prior to Execution

During Execution

1st data phase

write_strobes[0]=0b1010

->

write_strobes[0]=0b0010

2nd data phase

write_strobes[1]=0b1010

->

write_strobes[1]=0b1000

3rd data phase

write_strobes[2]=0b1010

->

write_strobes[2]=0b0010