Master_ready_delay_mode – Altera Mentor Verification IP Altera Edition AMBA AXI3/4TM User Manual

Page 162

Mentor VIP AE AXI3/4 User Guide, V10.2b

144

SystemVerilog Tutorials

Verifying a Slave DUT

September 2013

•

to handle the delay of

the write response channel BREADY signal and the read data channel RREADY signals,

respectively.

•

to set the

delay of the BREADY and RREADY signals

•

A

variable to configure the behavior of the handshake

signals *VALID to *READY delay.

The following sections described the main tasks and variables:

master_ready_delay_mode

The master_ready_delay_mode variable holds the configuration that defines the starting point

of any delay applied to the RREADY and BREADY signals. It can be configured to the

enumerated type values of AXI4_VALID2READY (default) or AXI4_TRANS2READY.

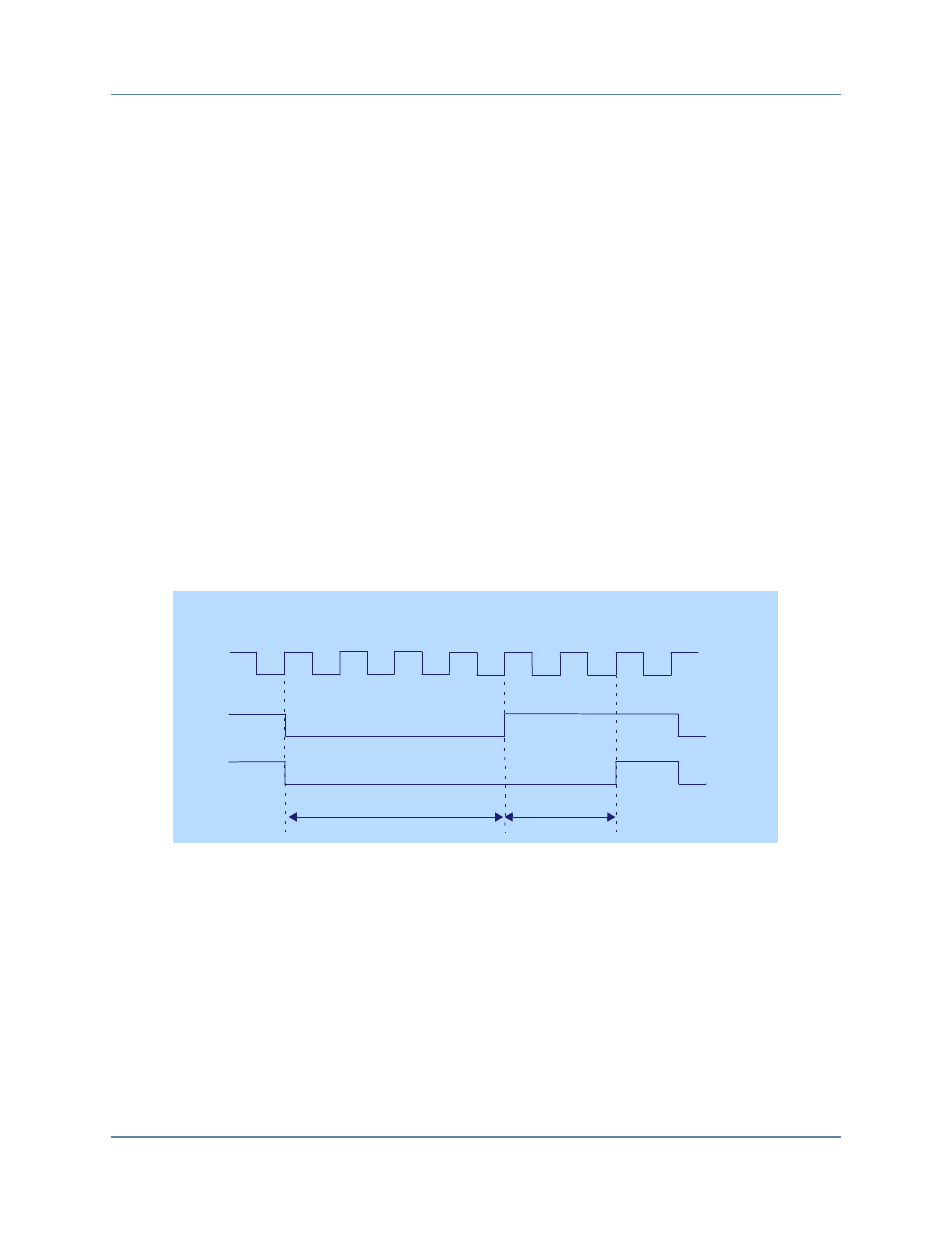

The default configuration (master_ready_delay_mode = AXI4_VALID2READY) corresponds to

the delay measured from the positive edge of ACLK when *VALID is asserted.

shows

how to achieve a *VALID before *READY handshake, respectively.

Figure 6-2. master_ready_delay_mode = AXI4_VALID2READY

The nondefault configuration (master_ready_delay_mode = AXI4_TRANS2READY)

corresponds to the delay measured from the completion of a previous transaction phase

(*VALID and *READY both asserted).

shows how to achieve a *READY before

*VALID handshake.

*VALID

*READY

ACLK

*_valid_delay = 4

*_ready_delay = 2