Verifying a master dut, Axi3 bfm slave test program, In the – Altera Mentor Verification IP Altera Edition AMBA AXI3/4TM User Manual

Page 642: Tutoria

Mentor VIP AE AXI3/4 User Guide, V10.2b

622

VHDL Tutorials

Verifying a Master DUT

September 2013

Verifying a Master DUT

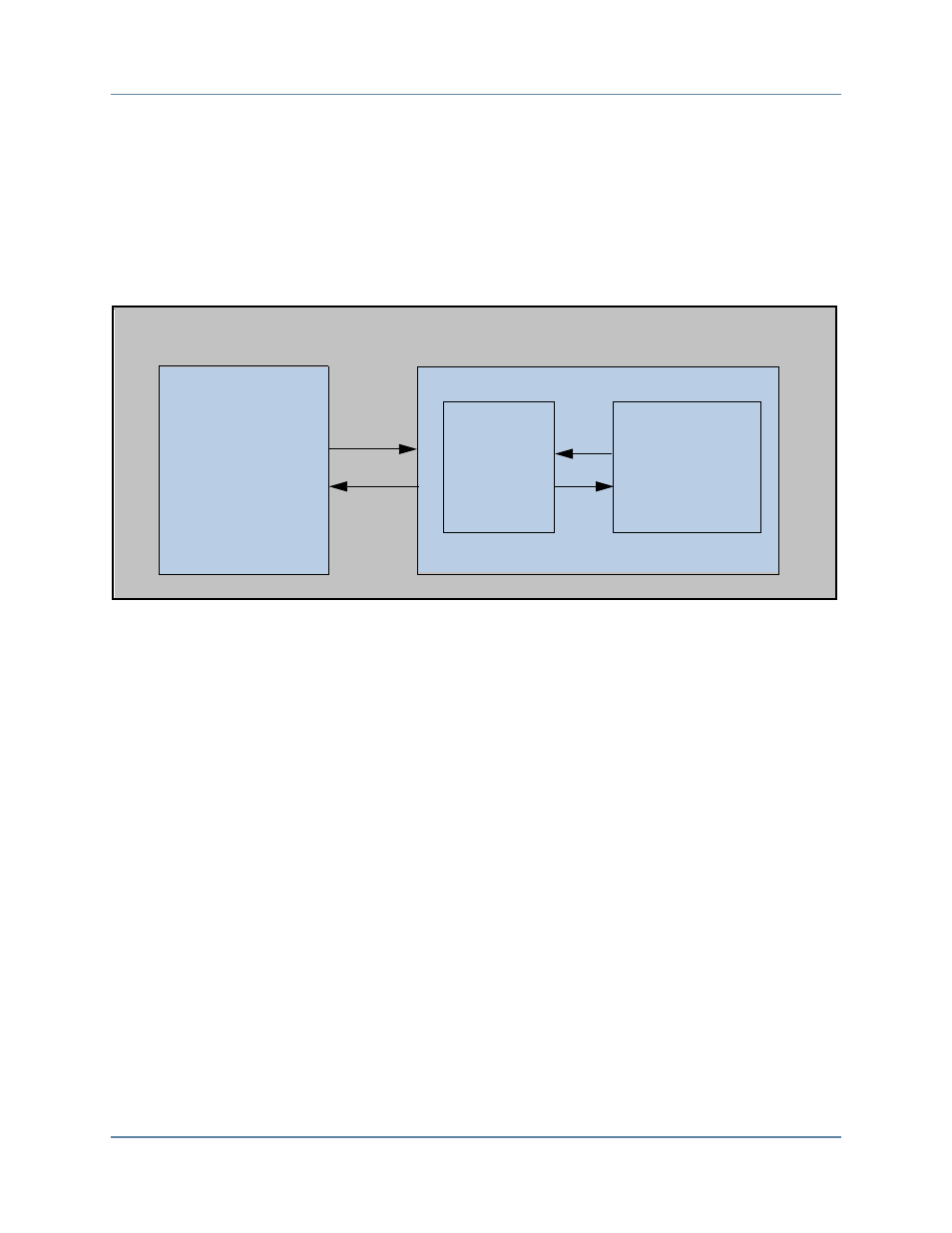

A master DUT component is connected to a slave BFM at the signal-level. A slave test program,

written at the transaction-level, generates stimulus via the slave BFM to verify the master DUT.

illustrates a typical top-level testbench environment.

Figure 11-2. Master DUT Top-level Testbench Environment

In this example the slave test program is a simple memory model.

A top-level file instantiates and connects all the components required to test and monitor the

DUT, and controls the system clock (ACLK) and reset (ARESETn) signals.

AXI3 BFM Slave Test Program

The Slave Test Program is a memory model and contains two APIs: an “

AXI3 Advanced Slave API Definition

AXI3 Basic Slave API Definition

allows you to create a wide range of stimulus scenarios to

test a master DUT. This simple API design illustrates the creation of slave stimulus based on the

default response of OKAY to master read and write transactions.

AXI3 Advanced Slave API Definition

allows you to create additional response scenarios to

transactions. For example, a successful exclusive transaction requires an EXOKAY response.

For a complete code listing of the Slave Test Program APIs, refer to the

Program

Test

Slave

BFM

Master

DUT

Slave

Top-level File