Axi4 assertions, Refer to – Altera Mentor Verification IP Altera Edition AMBA AXI3/4TM User Manual

Page 698

Mentor VIP AE AXI3/4 User Guide, V10.2b

678

Assertions

AXI4 Assertions

September 2013

AXI4 Assertions

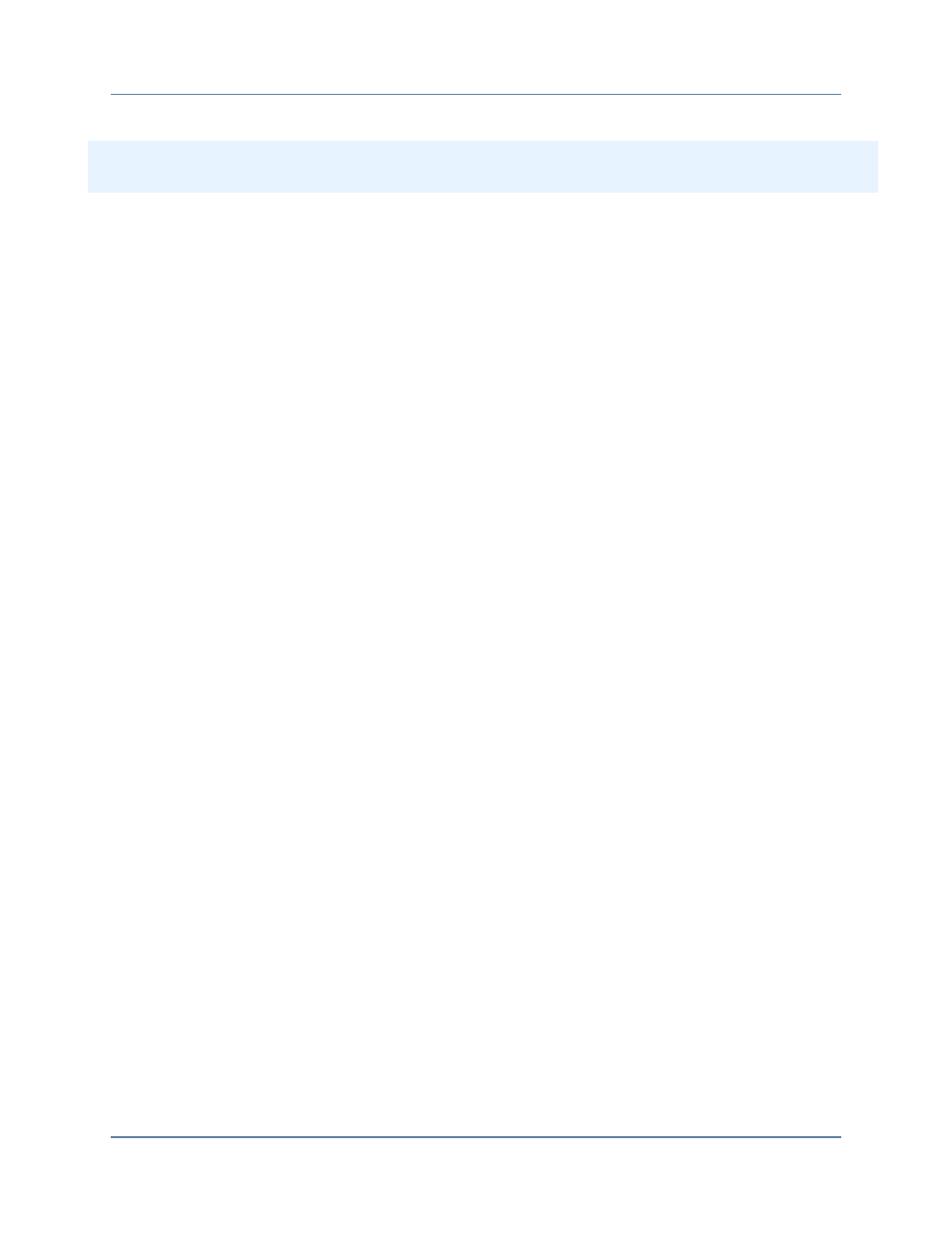

The AXI4 Master, Slave, and Monitor BFMs all support error checking with the firing of one or

more assertions when a property defined in the AMBA AXI Protocol Specification has been

violated. Each assertion can be individually enabled/disabled using the set_config() function for

Error

Code

Error Name

Description

Property

Ref

AXI3-

60193

AXI_EXCL_WR_WHILE_EXCL_RD_IN_

PROGRESS_SAME_ID

Master starts an exclusive write burst while

exclusive read burst with same ID tag is in

progress.

A7.2.4

AXI3-

60194

AXI_ILLEGAL_LENGTH_READ_BURST

Read address phase burst_length has an

illegal value.

A3.4.1

AXI3-

60195

AXI_ILLEGAL_LENGTH_WRITE_BURST

Write address phase burst_length has an

illegal value.

A3.4.1

AXI3-

60196

AXI_ARREADY_NOT_ASSERTED_

AFTER_ARVALID

Once ARVALID has been asserted,

ARREADY should be asserted within

config_max_latency_ARVALID_assertion_to

_ARREADY clock periods.

AXI3-

60197

AXI_BREADY_NOT_ASSERTED_

AFTER_BVALID

Once BVALID has been asserted, BREADY

should be asserted within

config_max_latency_BVALID_

assertion_to_BREADY clock periods.

AXI3-

60198

AXI_AWREADY_NOT_ASSERTED_

AFTER_AWVALID

Once AWVALID has been asserted,

AWREADY should be asserted within

config_max_latency_AWVALID_assertion_to

_AWREADY clock periods

AXI3-

60199

AXI_RREADY_NOT_ASSERTED_

AFTER_RVALID

Once RVALID has been asserted, RREADY

should be asserted within

config_max_latency_RVALID_assertion_to_

RREADY clock periods

AXI3-

60200

AXI_WREADY_NOT_ASSERTED_

AFTER_WVALID

Once WVALID has been asserted, WREADY

should be asserted within

config_max_latency_WVALID_assertion_to_

WREADY clock periods

AXI3-

60201

AXI_DEC_ERR_ILLEGAL_FOR_

MAPPED_SLAVE_ADDR

Slave receives a burst to a mapped address

but responds with DECERR (signalled by

AXI_DECERR).

A3.4.4

AXI3-

60202

AXI_PARAM_READ_REORDERING_

DEPTH_EQUALS_ZERO

The user-supplied

config_read_data_reordering_depth should

be greater than zero.

A5.3.1

AXI3-

60203

AXI_PARAM_READ_REORDERING_

DEPTH_EXCEEDS_MAX_ID

The user-supplied

config_read_data_reordering_depth exceeds

the maximum possible value, as defined by

the AXI_ID_WIDTH parameter.

A5.3.1

AXI3-

60204

AXI_READ_REORDERING_VIOLATION

The arrival of a read response has exceeded

the read reordering depth.

A5.3.1

Table A-1. AXI3 Assertions (cont.)