Altera Stratix GX Transceiver User Manual

Page 110

4–28

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

SONET Mode MegaWizard Plug-In Manager

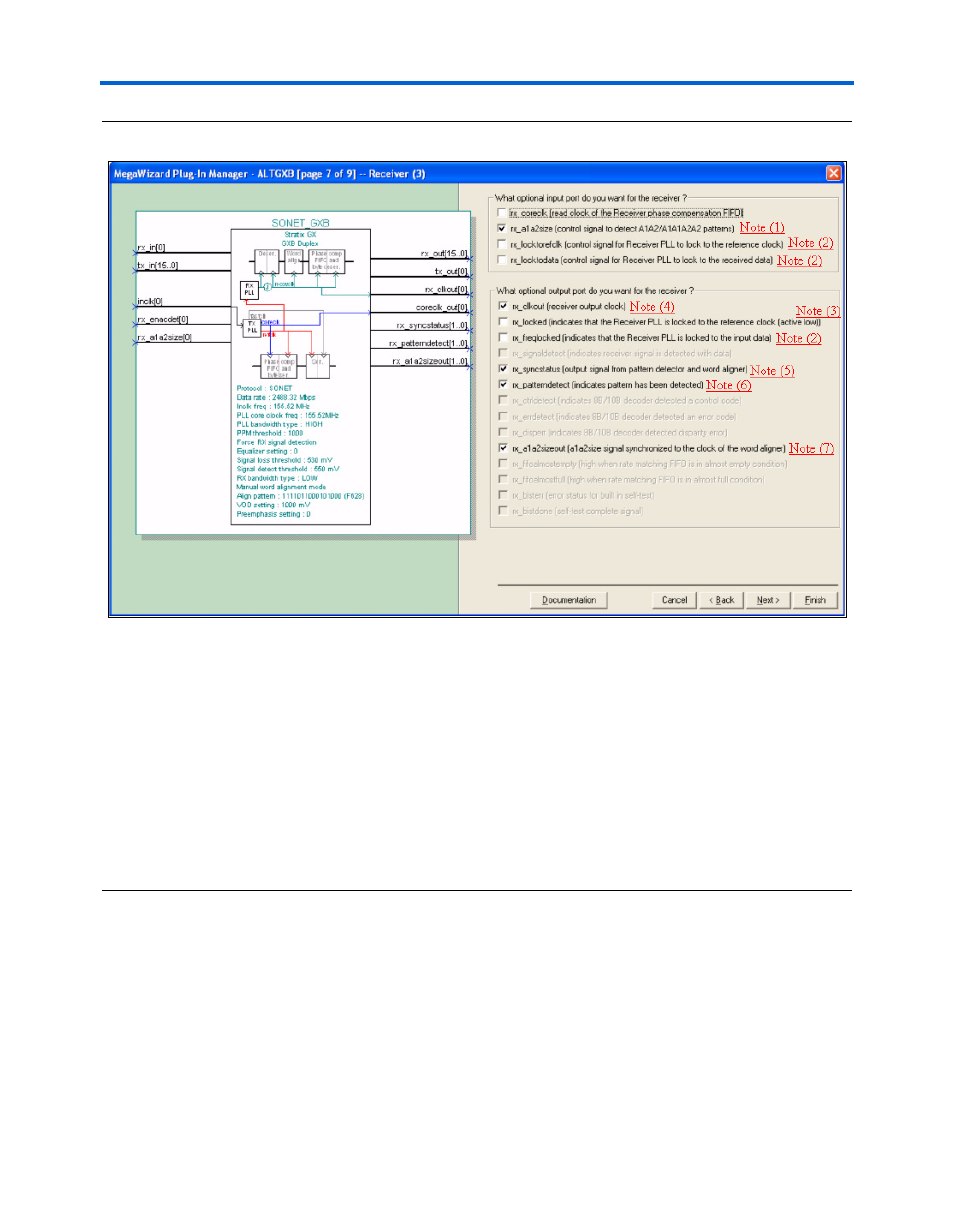

Figure 4–21. MegaWizard Plug-In Manager - ALTGXB (Page 7 of 9) - Receiver (3)

–

Notes to

:

(1)

Indicates to the word aligner to either align to an A1A2 or A1A1A2A2 pattern. Low = A1A2, High = A1A1A2A2.

(2)

For more information, refer to the Stratix GX Analog Description chapter.

(3)

Transmitter PLL and receiver PLL lock indicator. For

pll_locked

, High = transmitter PLL locked to reference

clock. For

rx_locked,

Low = receiver PLL locked to reference clock.

(4)

Receiver recovered clock output. There is one recovered clock available per receiver channel.

(5)

Indicates when the word aligner has aligned to the byte boundary. The

rx_syncstatus

signal goes high for

one

rx_clkout

period when the word aligner aligns to the new byte boundary. In 16-bit mode, each high and

low byte has a separate

rx_syncstatus

signal.

(6)

Rx_patterndetect

is similar to

rx_syncstatus

, with the exception that the

rx_patterndetect

asserts only when the word alignment pattern appears in the data stream within the synchronized byte boundary.

(7)

The

rx_a1a2sizeout

is a loopback of the

rx_a1a2size

signal that is synchronized with the current byte

from the word aligner.