Loopback, Built-in self test, Figure 1–5 – Altera Stratix GX Transceiver User Manual

Page 17

Altera Corporation

1–9

January 2005

Stratix GX Transceiver User Guide

Introduction

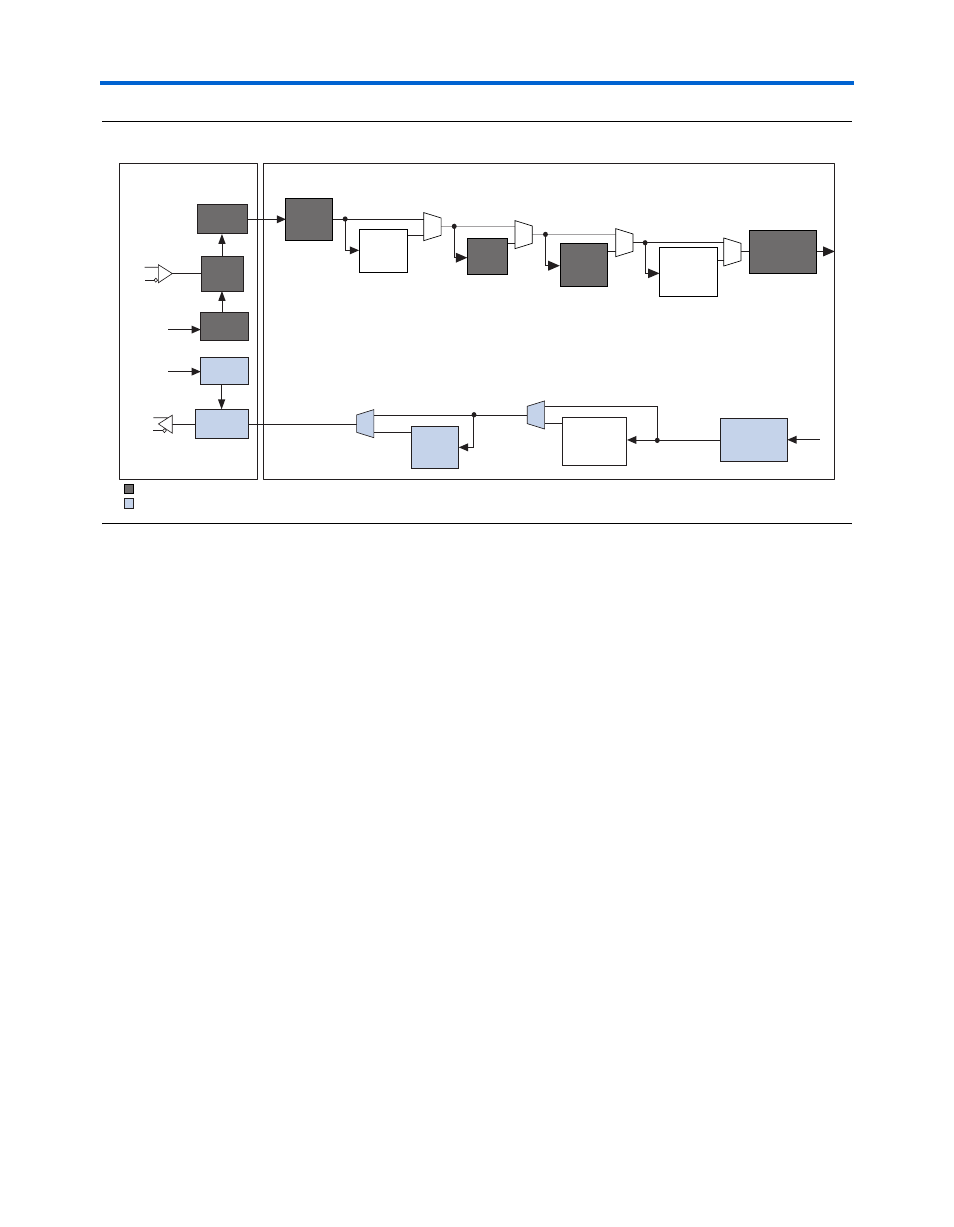

Figure 1–5. Block Diagram of a Duplex Channel Configured in GigE Mode

Loopback

There are three different loopback modes to use in the gigabit transceiver

block to allow for a complete method of in-system verification. The

loopback modes are versatile and robust enough to accommodate all

protocols and let you to choose whether to retime the data.

Built-In Self Test

The gigabit transceiver block contains several features that simplify

design verification. An embedded PRBS pattern generator provides a

bitstream pattern that you can use to test the device and board

connections. The PRBS pattern generator works with a PRBS receiver to

implement a full self-test path. Additionally, serial and parallel loopback

paths let you test the FPGA logic without monitoring external signals.

The reverse loopback path enables external system testing with minimal

device interaction.

Word

Aligner

Phase

Compensation

FIFO Buffer

Deserializer

Serializer

8B/10B

Decoder

Channel

Aligner

Byte

Deserializer

8B/10B

Encoder

Reference

Clock

Reference

Clock

Byte

Serializer

Phase

Compensation

FIFO Buffer

Rate

Matcher

Digital Section

Analog Section

Receiver

PLL

Transmitter

PLL

Clock

Recovery

Unit

Receiver

Transmitter