Altera Stratix GX Transceiver User Manual

Page 74

3–28

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

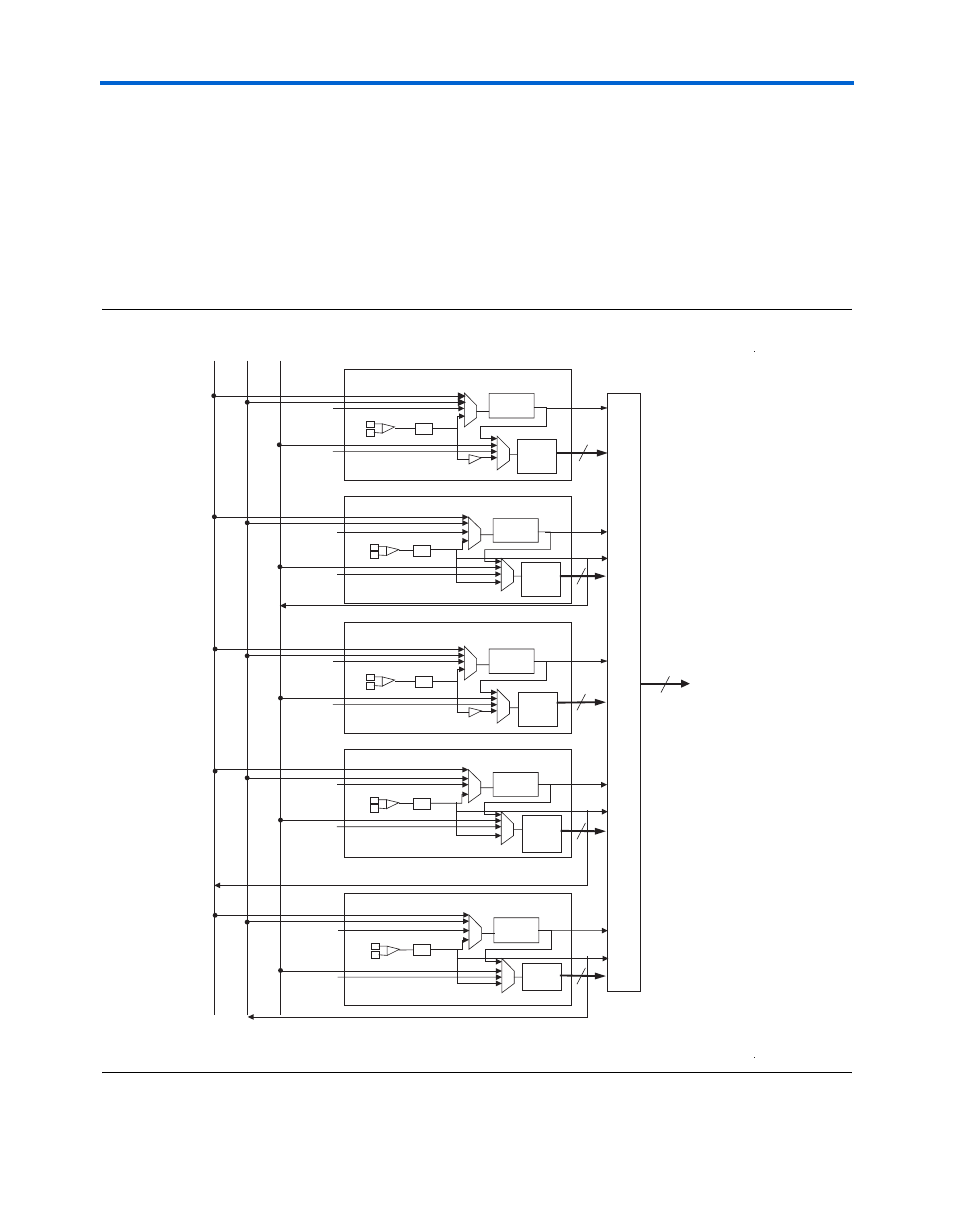

Basic Mode Clocking

shows the transceiver routing with respect to inter-

transceiver lines for the EP1SGX40G Device. This device has an extra

transceiver block (4), which is in the middle of the row of transceiver

blocks. This information is important when placing REFCLKB pins. For

example, if a REFCLKB pin must feed a transmitter PLL using an inter-

transceiver line, the REFCLKB pin cannot be in transceiver block 1,

because IQ2 feeds only the receiver PLLs. REFCLKB is used for

transceiver block 2 and transceiver block 3.

Figure 3–24. Inter-Transceiver Line Connections for the EP1SGX40G Device

PLD

Global

Clocks

IQ0

IQ1

IQ2

16

Transceiver Block 2

TX PLL

IQ0

IQ1

Global Clks, I/O Bus, Gen Routing

Global Clks, I/O Bus, Gen Routing

IQ2

/2

Transceiver Block 3

TX PLL

IQ0

IQ1

Global Clks, I/O Bus, Gen Routing

Global Clks, I/O Bus, Gen Routing

IQ2

/2

TX PLL

IQ0

IQ1

Global Clks, I/O Bus, Gen Routing

Global Clks, I/O Bus, Gen Routing

IQ2

Transceiver Block 0

/2

Transceiver Block 1

TX PLL

IQ0

IQ1

Global Clks, I/O Bus, Gen Routing

Global Clks, I/O Bus, Gen Routing

IQ2

/2

TX PLL

IQ0

IQ1

Global Clks, I/O Bus, Gen Routing

Global Clks, I/O Bus, Gen Routing

IQ2

Transceiver Block 4

/2

4

4

4

4

4

4

Receiver

PLLs

4

Receiver

PLLs

4

Receiver

PLLs

4

Receiver

PLLs

4

Receiver

PLLs

refclkb

refclkb

refclkb

refclkb

refclkb