Altera Stratix GX Transceiver User Manual

Page 312

Advertising

C–2

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Known Issues

If the design is using the transmitter PLL output to drive any clock

into the core (any part of the device), asserting the rxanalogreset

signal of all four channels also resets the transmitter PLL and affects

the clock that feeds the core logic. This behavior is not modeled in the

Quartus II software simulation.

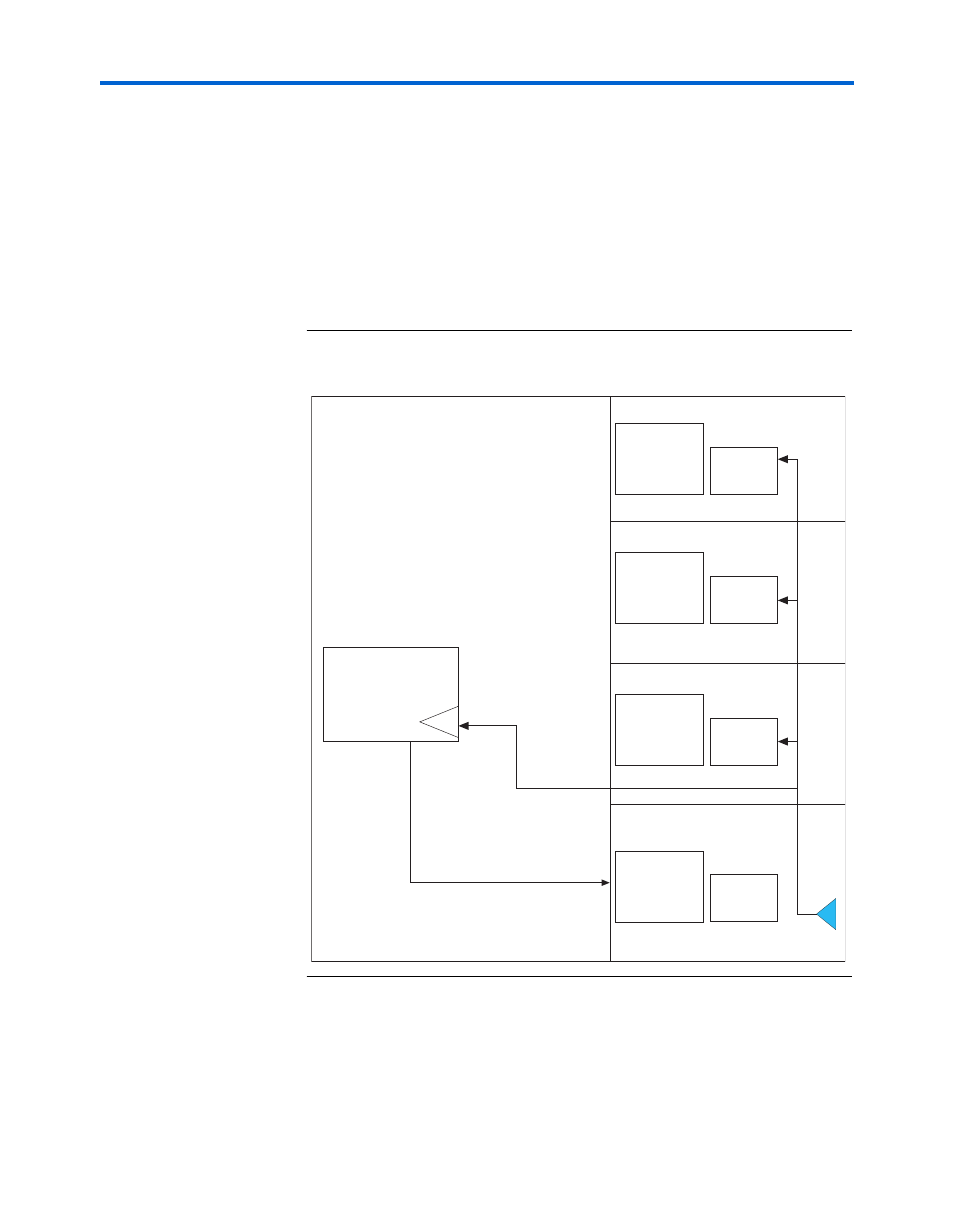

shows an example of a problem configuration using the

Stratix GX 25F device. This configuration is also applicable to all devices

in the Stratix GX device family.

Figure C–1. Example Configuration

Stratix GX25F Device

TX PLL

TX PLL

TX PLL

TX PLL

reset block

reset block

reset block

reset block

Reset

Controller

pll_areset

IQ1

GX Transceivers

PLD

Advertising