Altera Stratix GX Transceiver User Manual

Page 114

5–2

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

Introduction

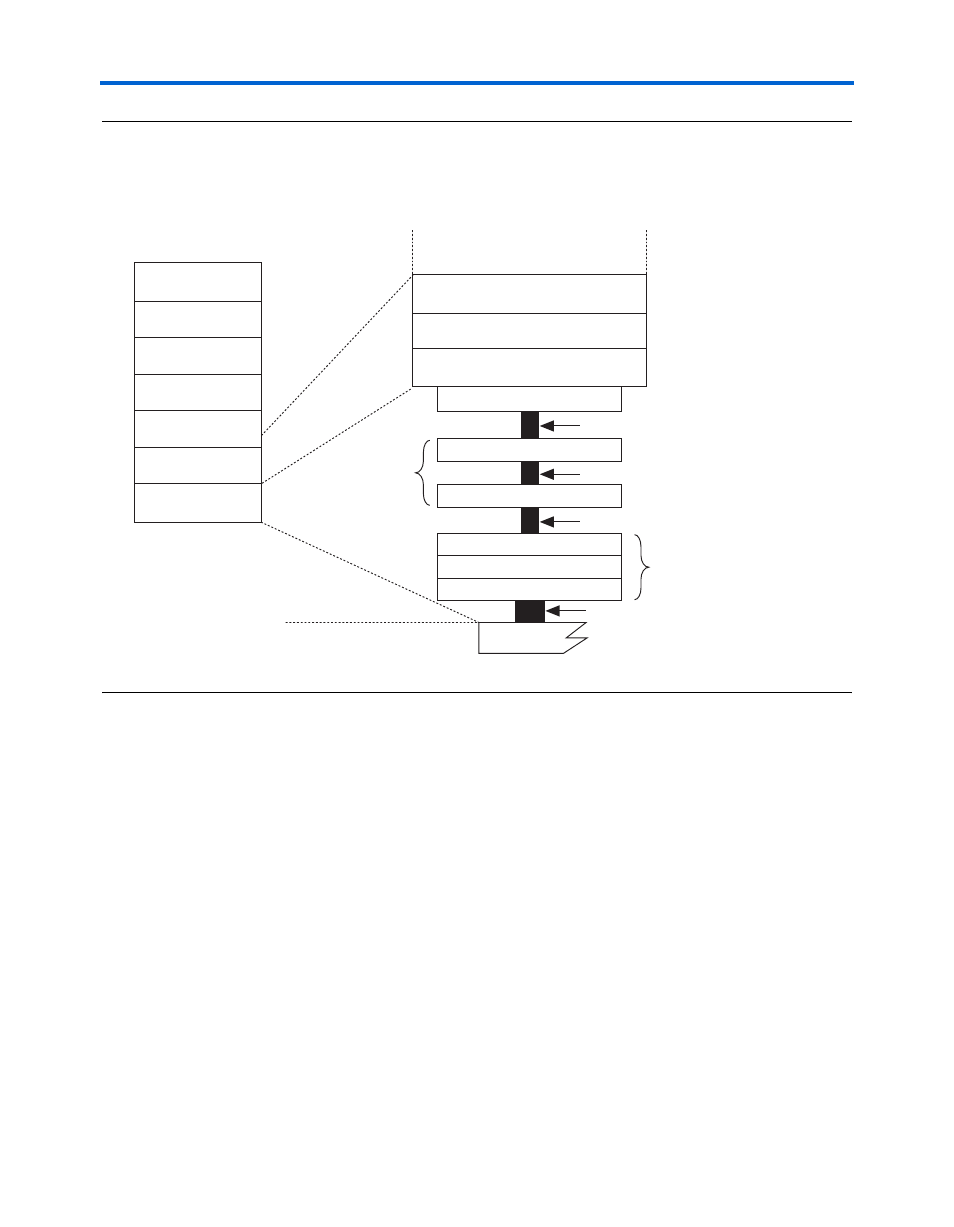

Figure 5–1. XGMII & XAUI Relationship to ISO/IEC Open Systems Interconnection (OSI) Reference Model &

IEEE 802.3 CSMA/CD LAN Model

As noted earlier, the XGMII interface consists of 4 lanes of 8 bits. At the

transmit side of the XAUI interface, the data and control characters are

converted within the XGXS into an 8B/10B encoded data stream. Each

data stream is then transmitted across a single differential pair running at

3.125 Gbps. At the XAUI receiver, the incoming data is decoded and

mapped back to the 32 bit XGMII format. This process provides a

transparent extension of the physical reach of the XGMII and also reduces

the interface pin count.

Lo

g

ical Link Control (LLC)

MAC Control (optional)

Media Access Control (MAC)

Application

Presentation

Session

Transport

Network

Data Link

Physical

OSI Reference

Model Layers

LAN Carrier Sense Multiple

Access/Collision Detect (CSMA/CD)

Layers

Hi

g

her Layers

Optional XGMII

Extender

Medium Dependent Interface

Medium

10 Gb/s

10 Gi

g

abit Media Independent Interface

10 Gi

g

abit Attachment Unit Interface

XGMII Extender Sublayer

Reconciliation

Physical Layer Device

XGMII Extender Sublayer

10 Gi

g

abit Media Independent Interface

Physical Medium Attachment

Physical Codin

g

Sublayer

Physical Medium Dependent