Control code encoding – Altera Stratix GX Transceiver User Manual

Page 173

Altera Corporation

6–19

January 2005

Stratix GX Transceiver User Guide

GigE Mode

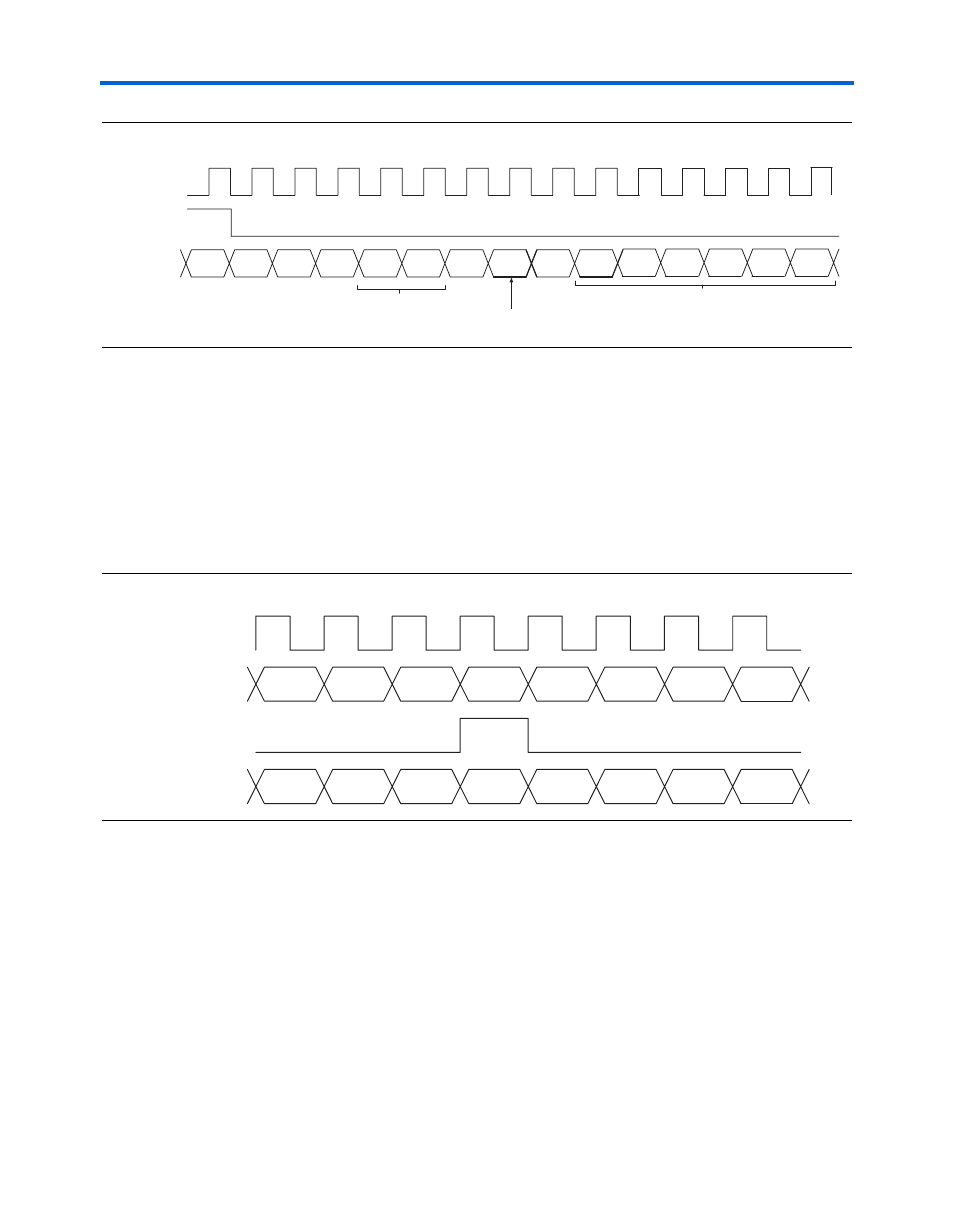

Figure 6–19. Even Number of /Dx.y/ Between Last Automatically Sent /K28.5/ & the First User-Sent /K28.5/

Control Code Encoding

The tx_ctrlenable[] signal determines when a control code must be

inserted in the encoded data flow. When the tx_ctrlenable[] signal

is low, the byte at tx_in[] is encoded as data. When the

tx_ctrlenable[]

signal is high, tx_in[] is encoded as a control

word. The waveform in

encoded as a control code. The rest are encoded as data.

Figure 6–20. Control Word Identification Waveform

The 8B/10B encoder does not check that the code word you entered is one

of the 12 valid codes. If an invalid control code is entered, the resulting

10-bit code is encoded as either invalid code (that does not map to a valid

/Dx.y/

or /Kx.y/ code), or valid /Dx.y/ code, depending on the value

entered.

An example is the invalid encoding of a /K24.1/ (data = 8’h38 +

tx_ctrlenable

= 1’b1). Depending on the current running disparity,

the /K24.1/ can be encoded to be 10’b0110001100 (0x18C), which is

equivalent to a /D24.6/+ (0xD8 from the RD+ column). An 8B/10B

decoder decodes this incorrectly (based on the 8B/10B Fibre Channel

specification).

clock

tx_out[9:0 ]

txdigitalreset

K28.5

xxx

K28.5

K28.5

K28.5

Dx.y

Dx.y

K28.5

Dx.y

K28.5

Dx.y

K28.5

D.xy

K28.5

Dx.y

First Ordered Set

Invalid Ordered Set

Even Number of /Dx.y/

Three Ordered Sets for Syncrhonization

clock

tx_in[7:0]

tx_ctrlenable

83

78

BC

BC

0F

00

BF

3C

D3.4

D24.3

D28.5

K28.5

D15.0

D0.0

D31.5

D28.1

Code Group