Sonet mode receiver architecture, Word aligner, Sonet mode receiver architecture –2 – Altera Stratix GX Transceiver User Manual

Page 84

4–2

Altera Corporation

Stratix GX Transceiver User Guide

January 2005

SONET Mode Receiver Architecture

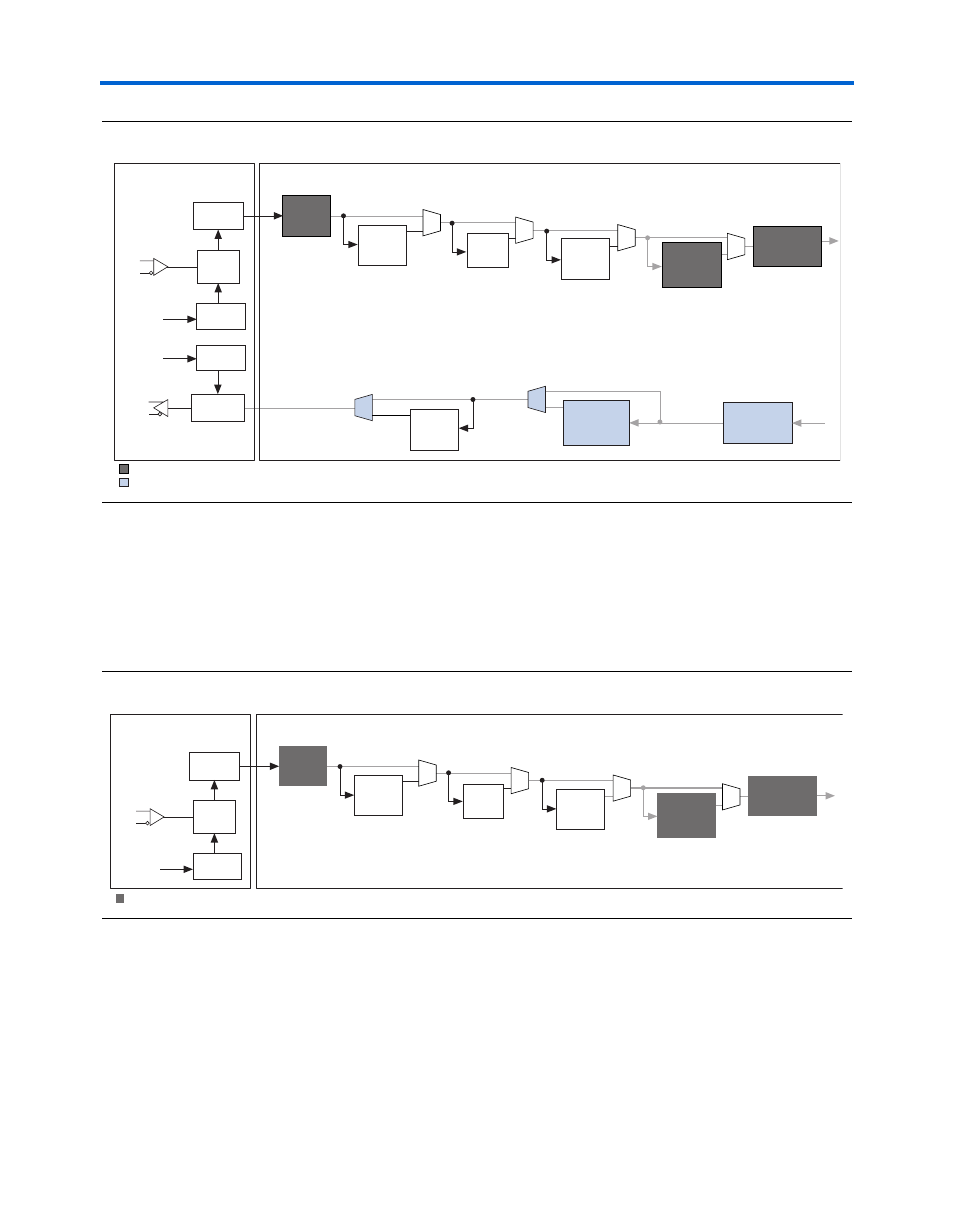

Figure 4–1. Block Diagram of Transceiver Channel Configured in SONET Mode

SONET Mode

Receiver

Architecture

shows the digital components of the Stratix GX receiver that

are active in SONET mode.

Figure 4–2. Block Diagram of Receiver Digital Components in SONET Mode

Word Aligner

For embedded clocking schemes, the clock is recovered from the

incoming data stream based on transition density of the data. This feature

eliminates the need to factor in receiver skew margins between the clock

and data. However, with this clocking methodology, the word boundary

of the re-timed data can be altered. Stratix GX transceivers offer an

Deserializer

Serializer

Word

Aligner

8B/10B

Decoder

Channel

Aligner

Byte

Deserializer

8B/10B

Encoder

Phase

Compensation

FIFO Buffer

Reference

Clock

Reference

Clock

Phase

Compensation

FIFO Buffer

Rate

Matcher

Digital Section

Analog Section

Receiver

PLL

Transmitter

PLL

Clock

Recovery

Unit

Receiver

Transmitter

Byte

Serializer

Deserializer

Word

Aligner

8B/10B

Decoder

Channel

Aligner

Byte

Deserializer

Phase

Compensation

FIFO Buffer

Reference

Clock

Rate

Matcher

Digital Section

Analog Section

Receiver

PLL

Clock

Recovery

Unit

Receiver